# Service Manual

These service instructions are for use by qualified personnel.

Please contact Fairlight or your distributor

before attempting any repairs

Copyright 1986, Fairlight Instruments Pty Ltd.

All rights reserved

Contents of this publication may not be reproduced in any form without the written permission of Fairlight Pty Ltd.

Specifications are subject to continual change and enhancement and Fairlight reserves the right to alter specifications without notice

Fairlight Pty Ltd., 15 Boundary Street, Rushcutters Bay, N.S.W. 2011

Sydney, Australia

Phone: (02) 331 6333, Telex: AA127998 'FAIRLT'

| CMI System 1                           |  |

|----------------------------------------|--|

| Digital Card Cage 2                    |  |

| Avrolo, Galookerojevi in 1985.         |  |

| Ancillary Boards (1984) 1984 (1984) 24 |  |

| Troubleshooting & 5 Diagnostics 5      |  |

| Miss Storetoe Devices                  |  |

| AMODONIARIO<br>Kayanorio               |  |

| Militare Keyroerrok                    |  |

|                                        |  |

## Contents

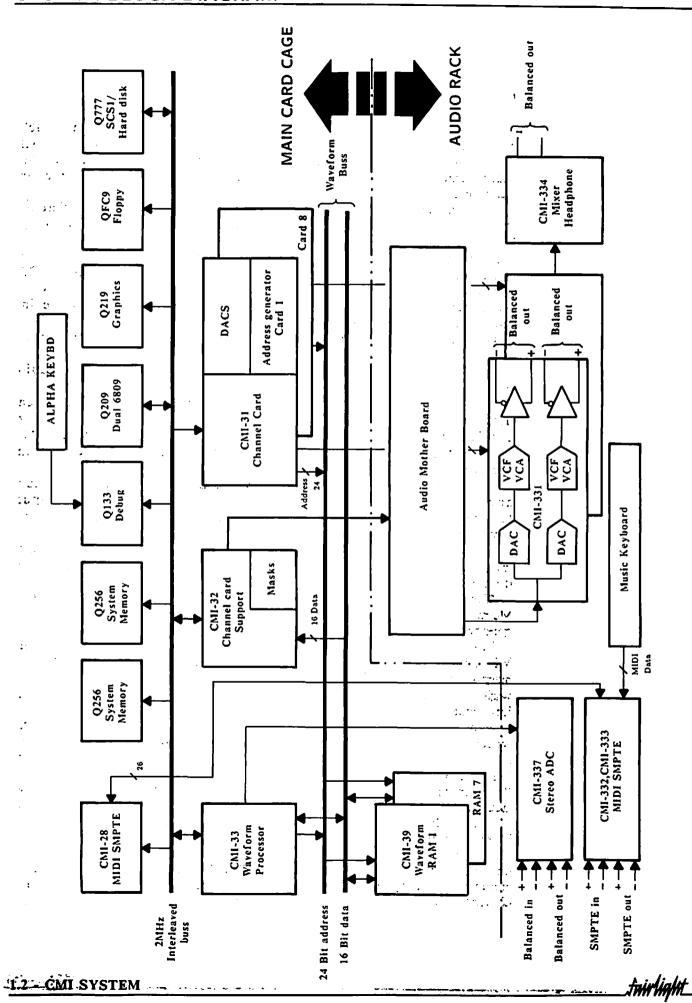

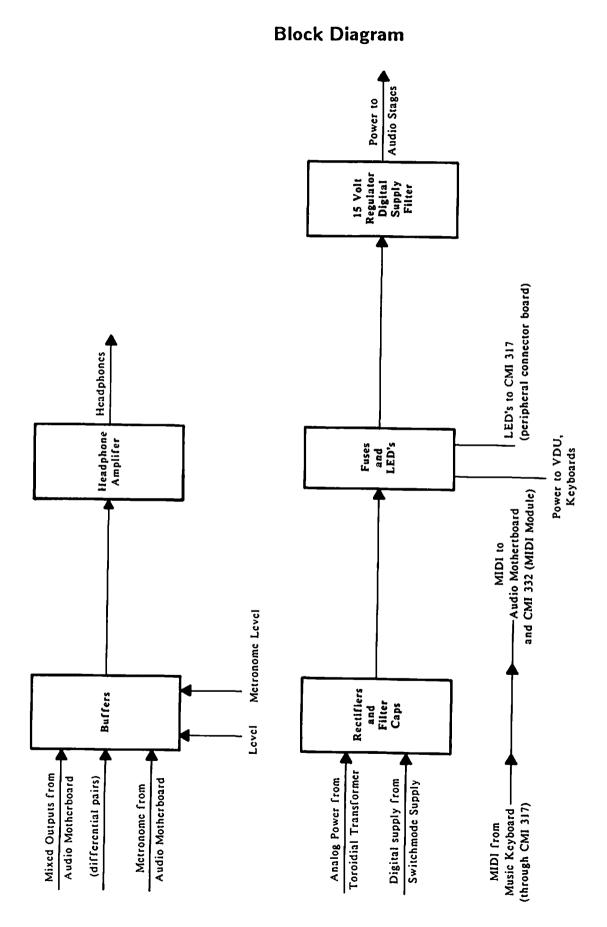

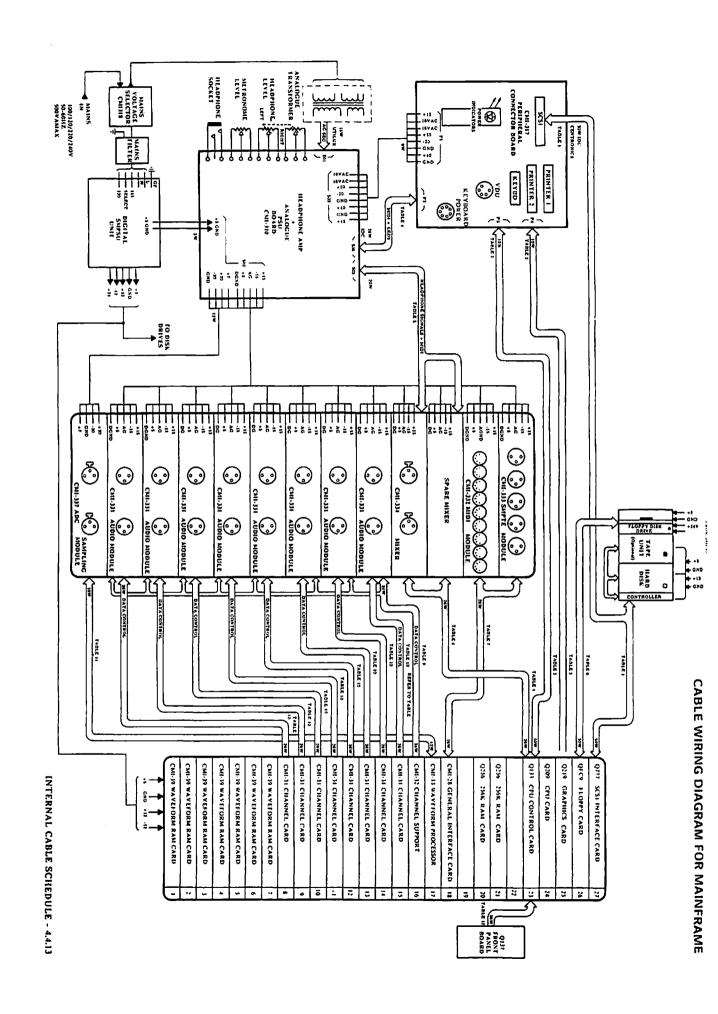

| System block diagram       | 1.2  |

|----------------------------|------|

| System overview            | 1.3  |

| Specifications             | 1.9  |

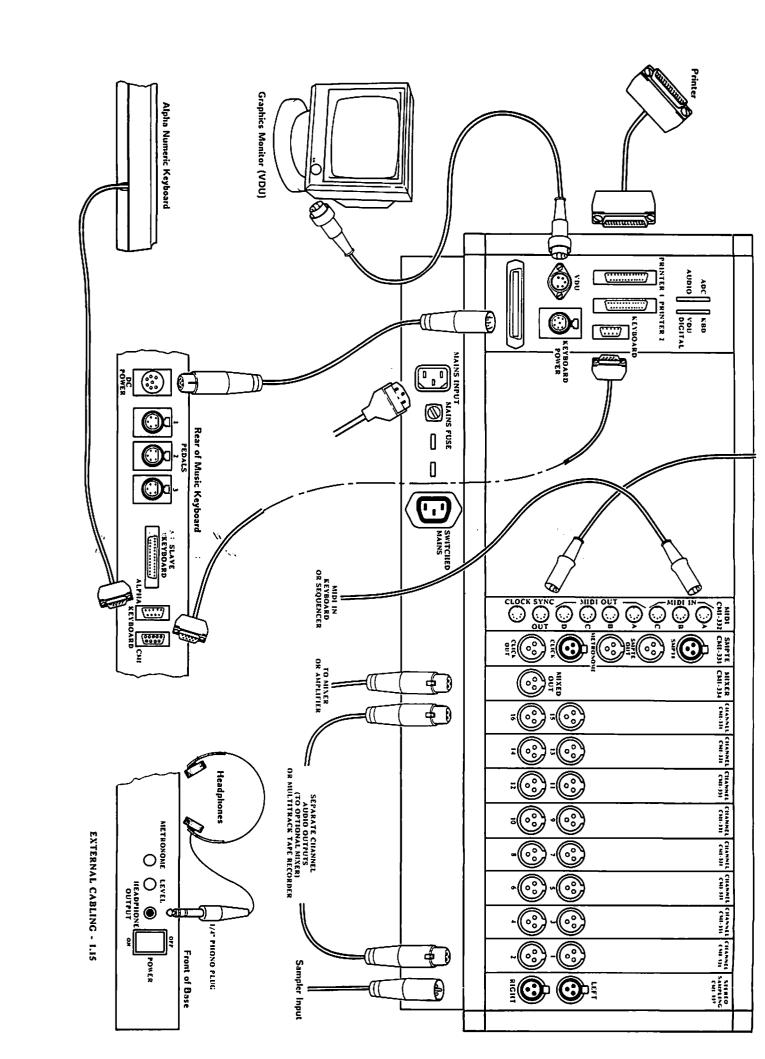

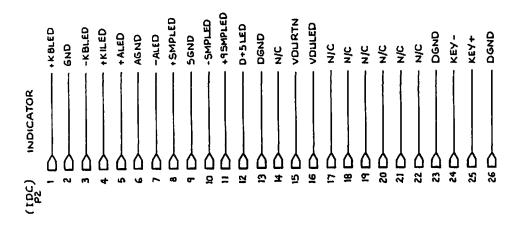

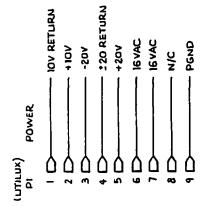

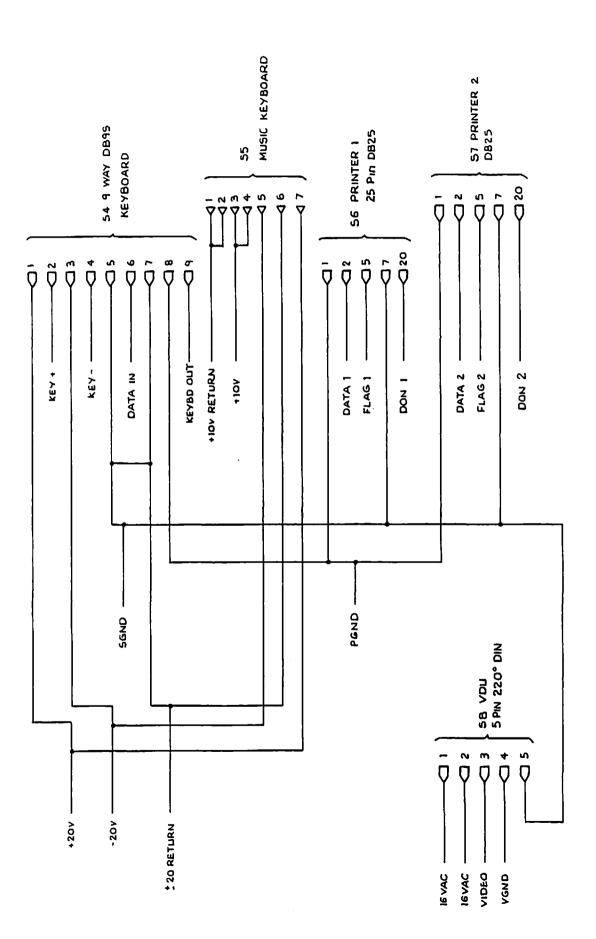

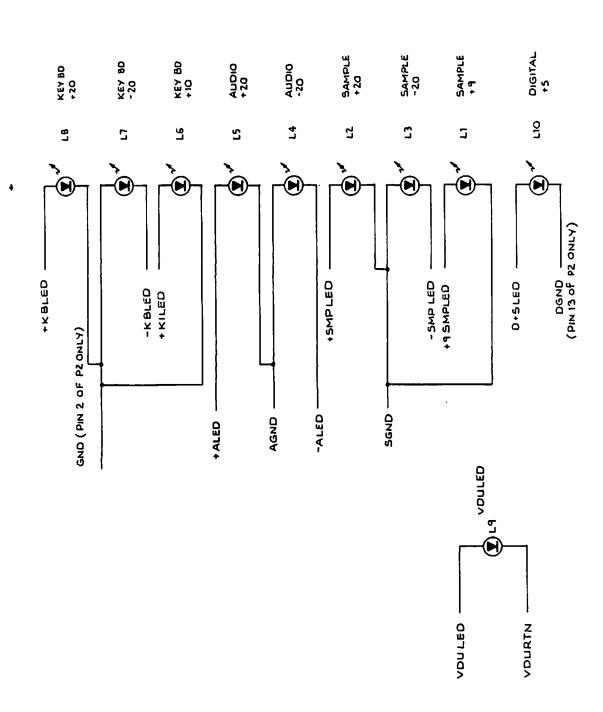

| External Cabling           | 1.11 |

| CMI III Connection diagram | 1.15 |

\_tairlight\_

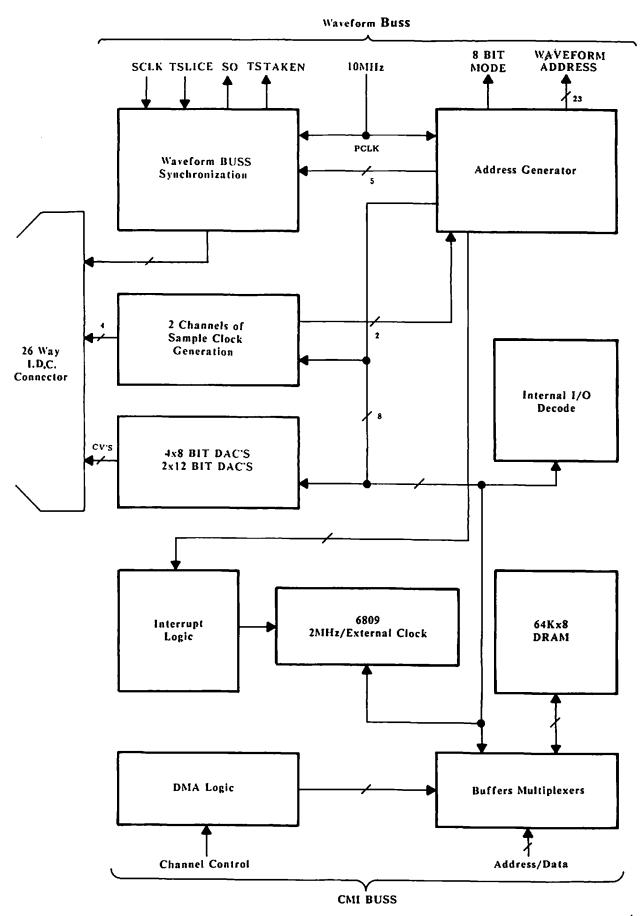

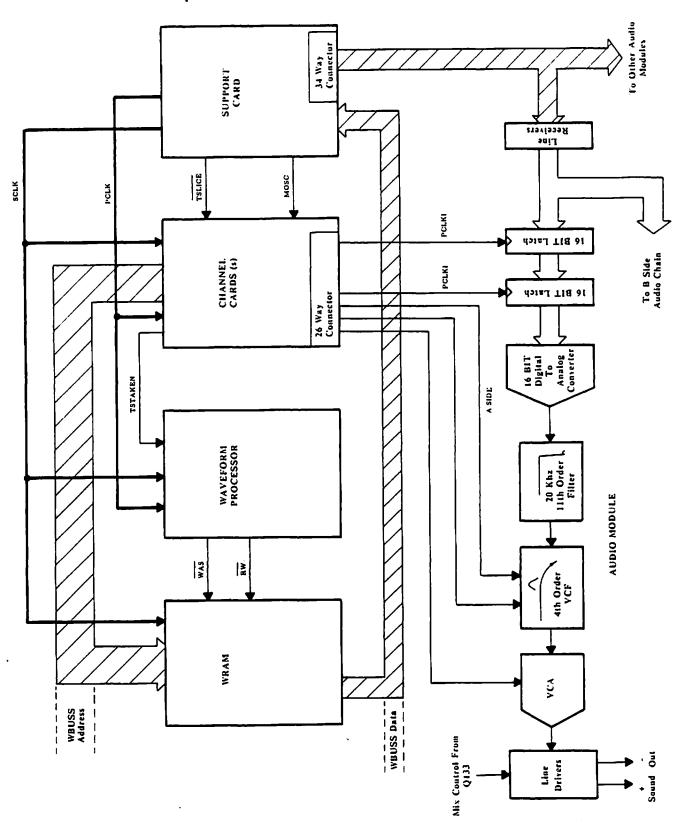

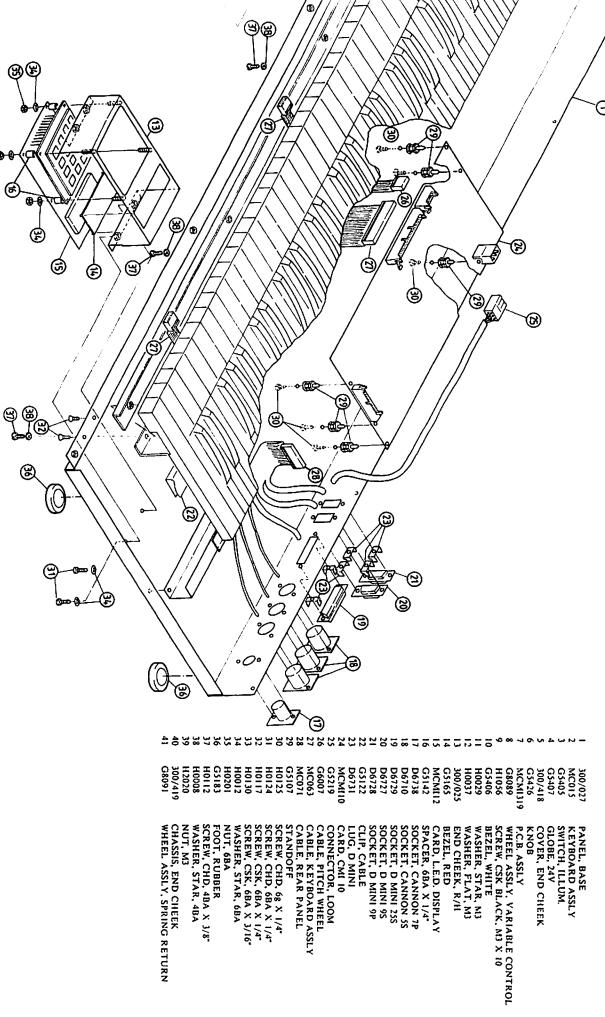

General Principles (Refer to Figure 1)

The C.M.I. is a complex special-purpose computer system which embraces many different hardware and software technologies. All processing and sound generation functions are performed by the Mainframe, while the Graphics Terminal and Keyboards serve as peripherals for operator interfacing.

The mainframe is capable of operating quite autonomously, that is, it is not reliant on any external connections for proper functioning. Under certain conditions it is possible for a fault condition in external peripherals such as keyboards to inhibit proper main frame operation, so the serviceperson should be wary of being misled. Of course, without the peripherals connected it is often hard to know if the system is functioning properly, but this point should be borne in mind when trouble-shooting.

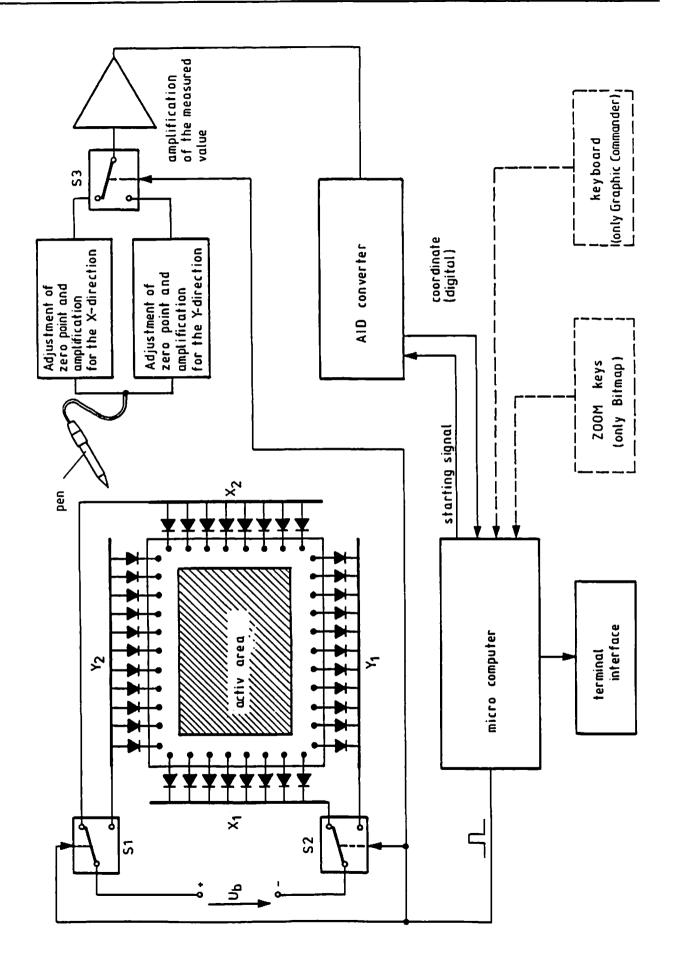

Operator input to the Mainframe comes from three sources: music keyboard, alphanumeric keyboard and graphics pad.

Output devices include the Graphics Display terminal and the audio outputs. A printer may also be used.

The heart of the system is the Central Processing Module, which uses two Motorola 6809 microprocessors in a dual-processor configuration. Both processors share a common buss called the CMI Buss or the CPU Buss which allows them both to communicate with the other processors in the Mainframe.

The Processor Control Module provides EPROM for system startup and bootstrap, RS-232C serial input from the keyboard, serial output to the keyboard and printer, and various other CPU support functions such as interrupt prioritisation.

Main program memory is provided by the 256K RAM card(s). This holds all the operational software, much of which is overlaid from disk as the code exceeds 256K.

The Floppy-disk and Hard disk (SCSI) controllers use Direct Memory Access (DMA) techniques to transfer data between main memory and the two floppy-disk drives.

The Graphics Display is a bit-mapped image of 16K bytes of VRAM. This is displayed as an array of 256 by 512 points. Special hardware provides support functions for automatic vector drawing, which considerably enhances the speed of displaying graphical information.

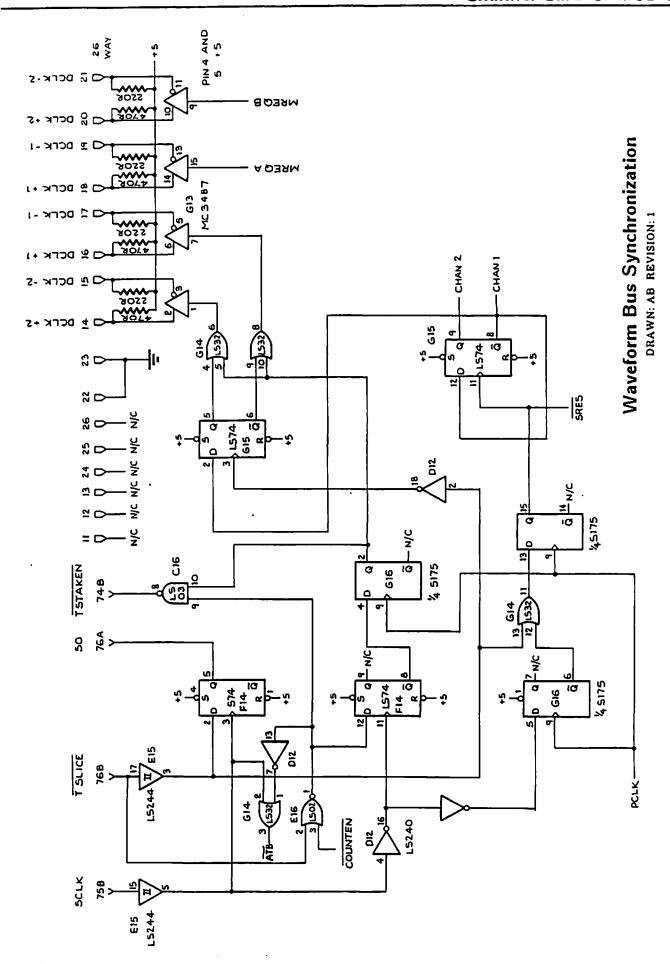

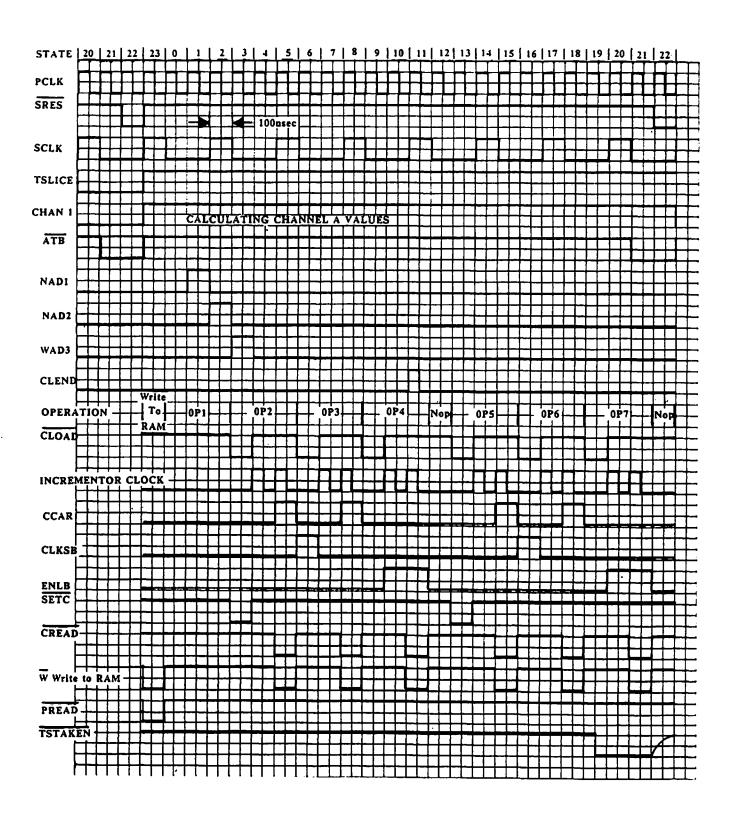

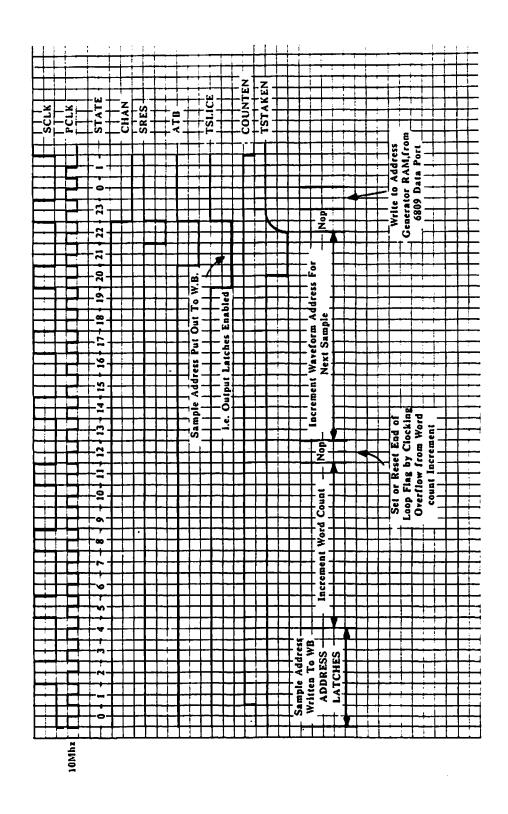

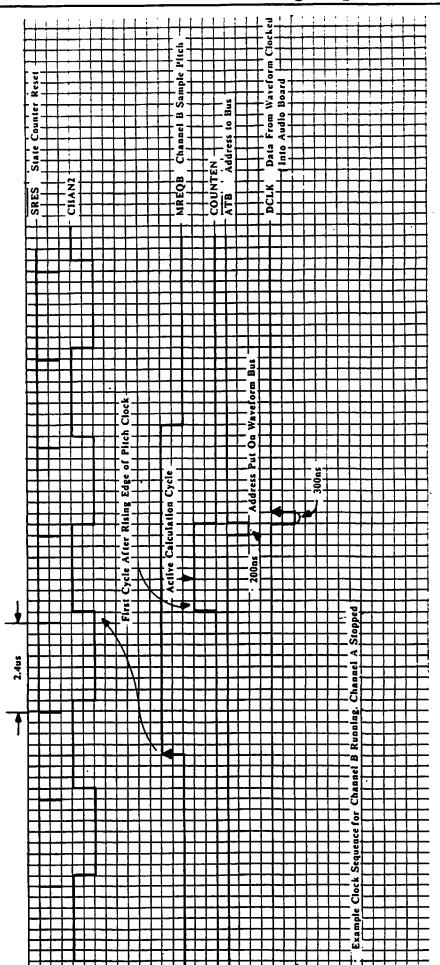

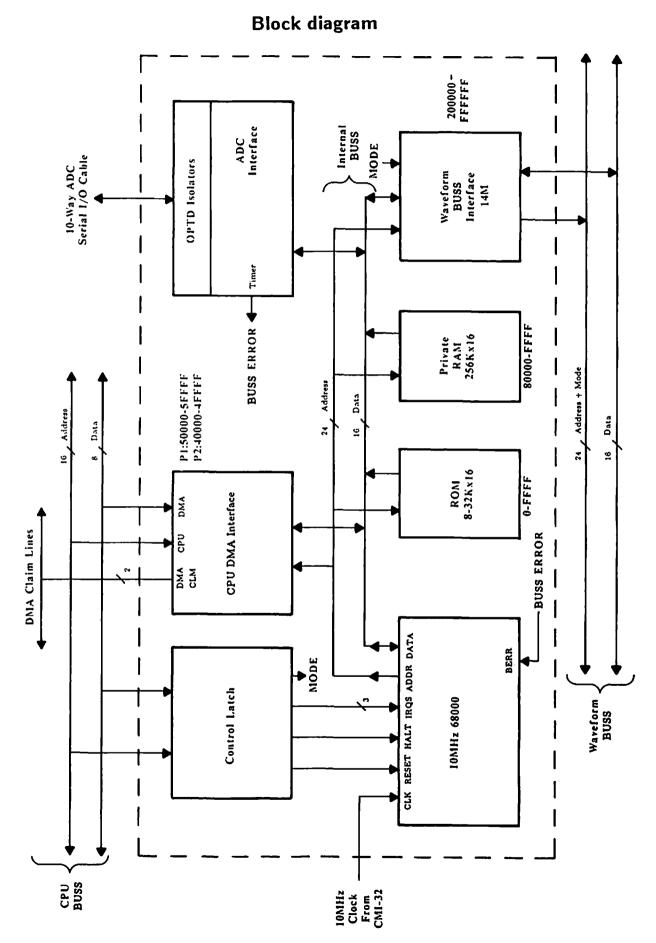

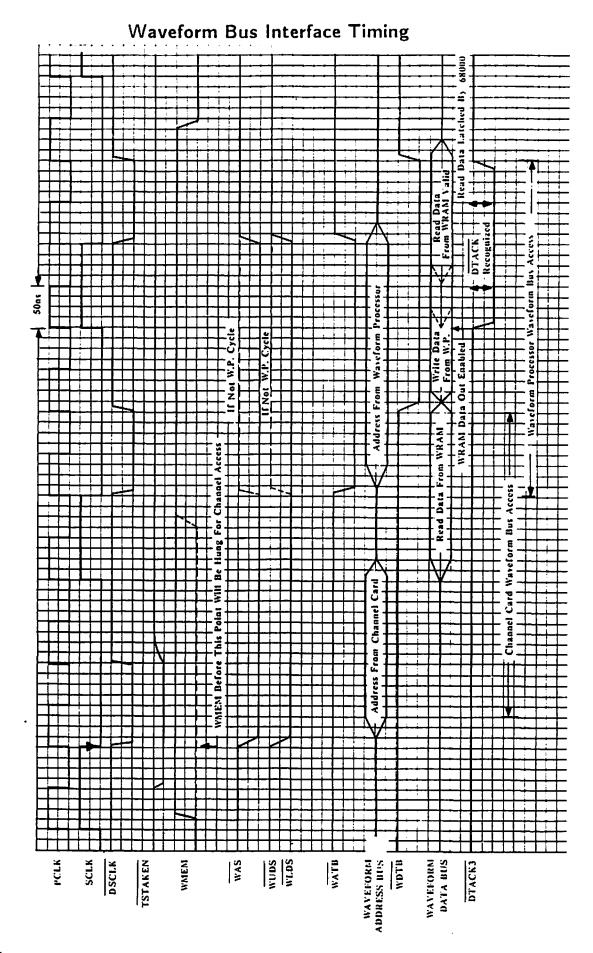

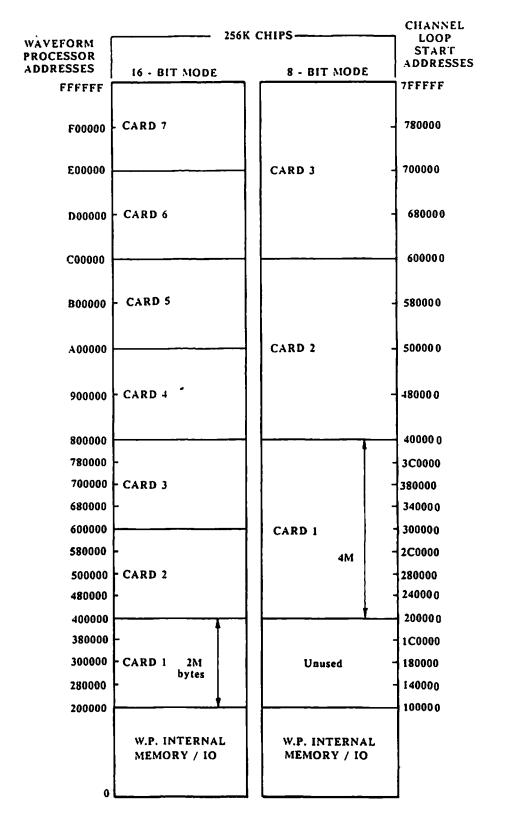

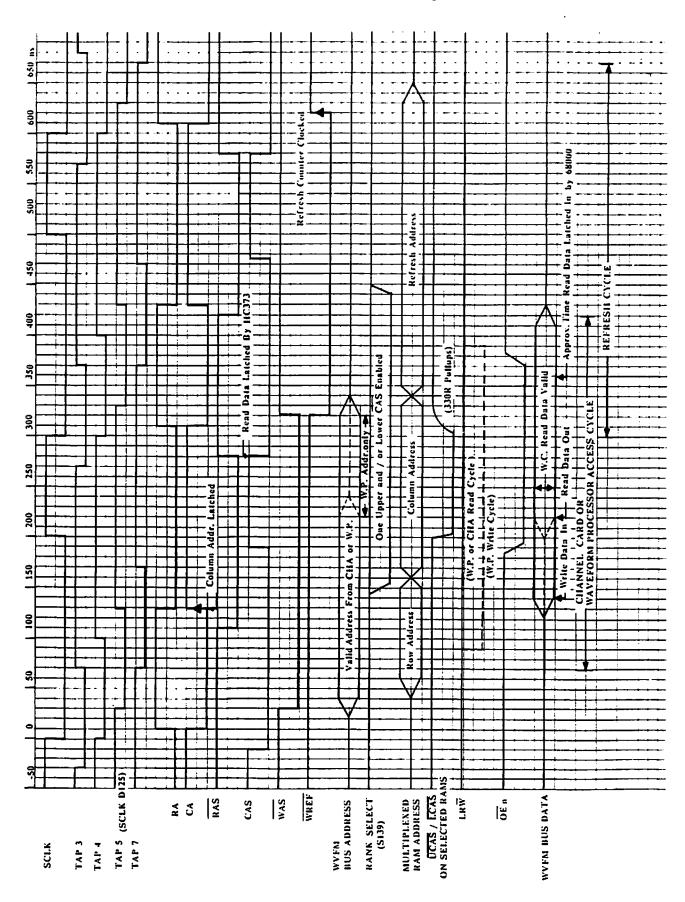

The digital section contains a second buss called the Waveform Buss which is entirely independent of the CPU buss and is dedicated to sound generation, manipulation and sampling. It has a 23 bit address buss, a 16 bit data buss, synchronous control lines and runs at 3.3 Mhz. It supports up to 14 megabytes of 16 bit waveform RAM. All RAM is accessible by all channel cards in cycles of 16 time slices. This allows 16 channels to run at a maximum of just under 200khz each. The Waveform Processor is the only device that can read and write to the Waveform RAM so it is responsible for loading, saving, sampling and manipulating sounds in waveform RAM. The channel cards only generate read cycles to get data from waveform RAM to the Audio Output modules. The actual waveform data read out of waveform

.twirlight\_

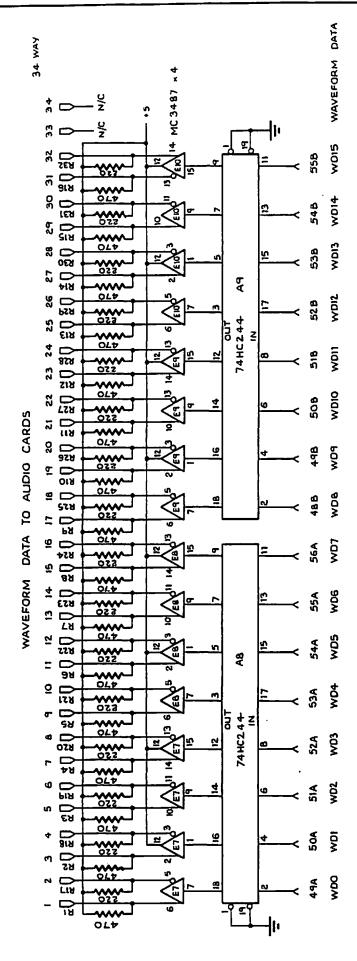

RAM in response to addresses generated by the channel cards do not return to the channel card but are picked up from the waveform buss by the Channel Support card and sent directly to the the Audio Motherboard and thence the Audio Output Modules. (see System block diagram)

Access to the waveform buss is prioritized in the order Channel cards, Waveform RAM refresh, then Waveform Processor. Channel cards are allowed access to the buss in a cyclic "round robin" manner. The channel card may or may not used its allocated time slice. Unused channel card time slices are allocated to refresh, then Waveform processor access.

The Waveform Processor and Channel cards reside on both CPU and Waveform busses so that they may be controlled by the CPU as well as accessing sounds in Waveform RAM.

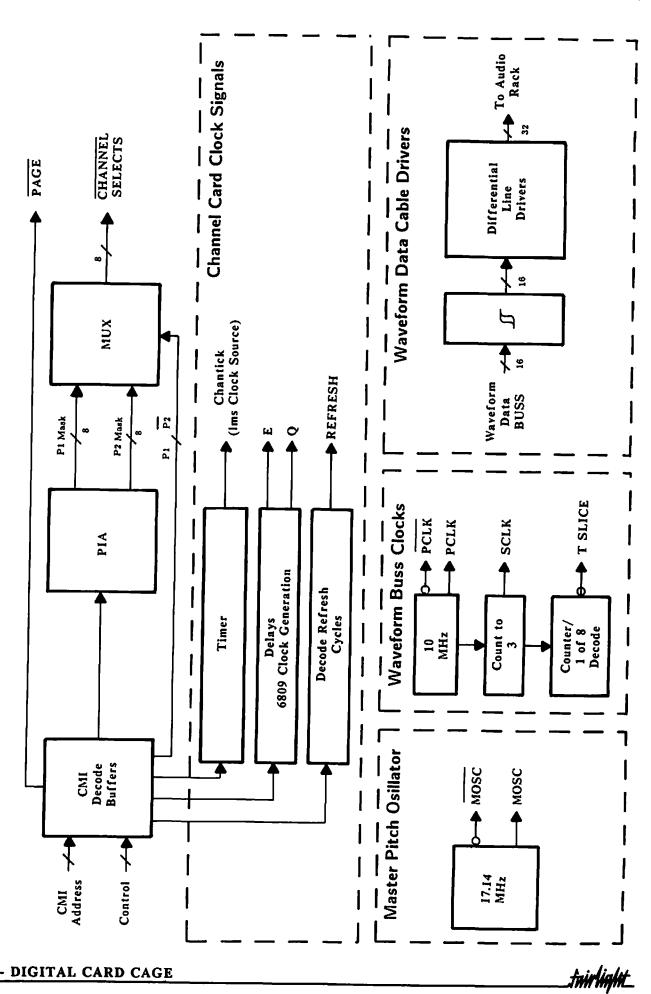

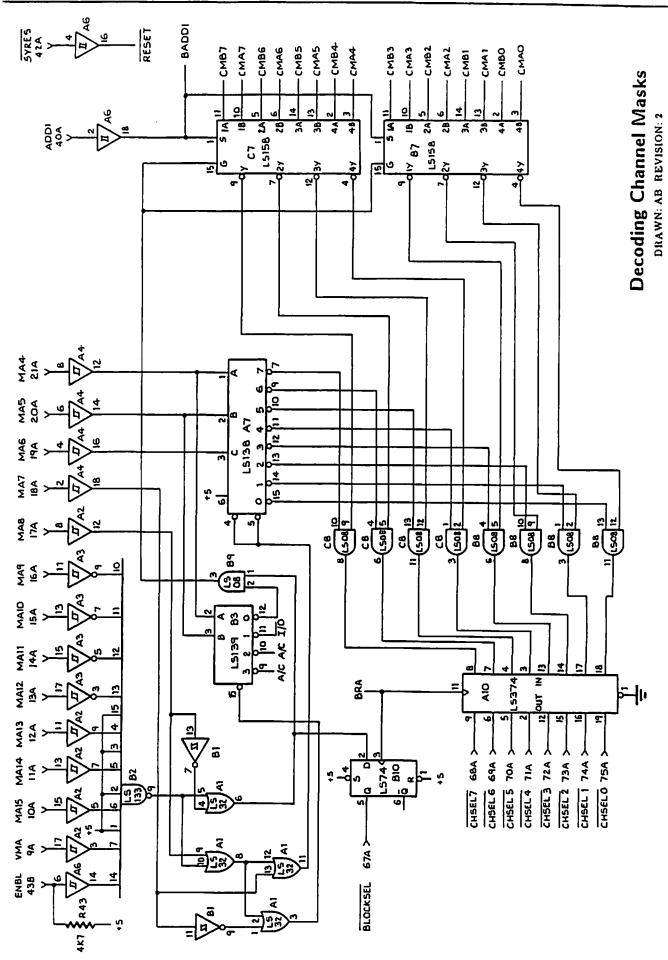

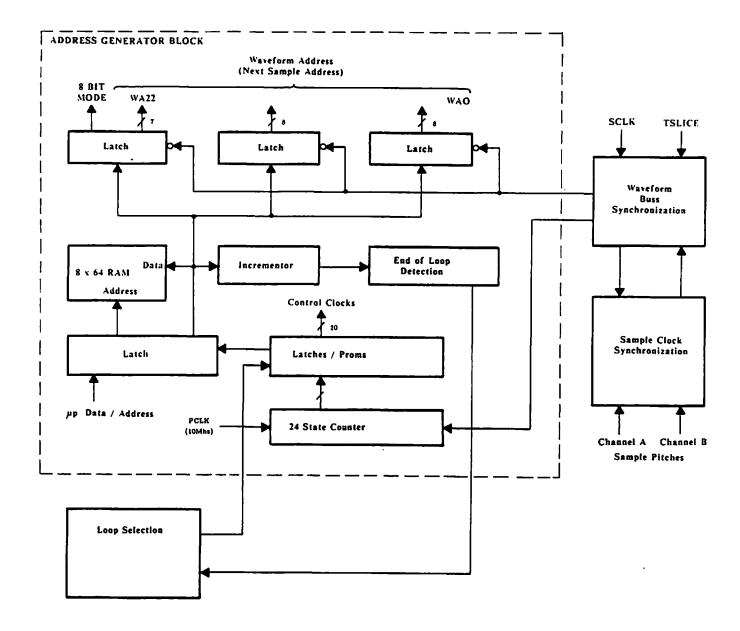

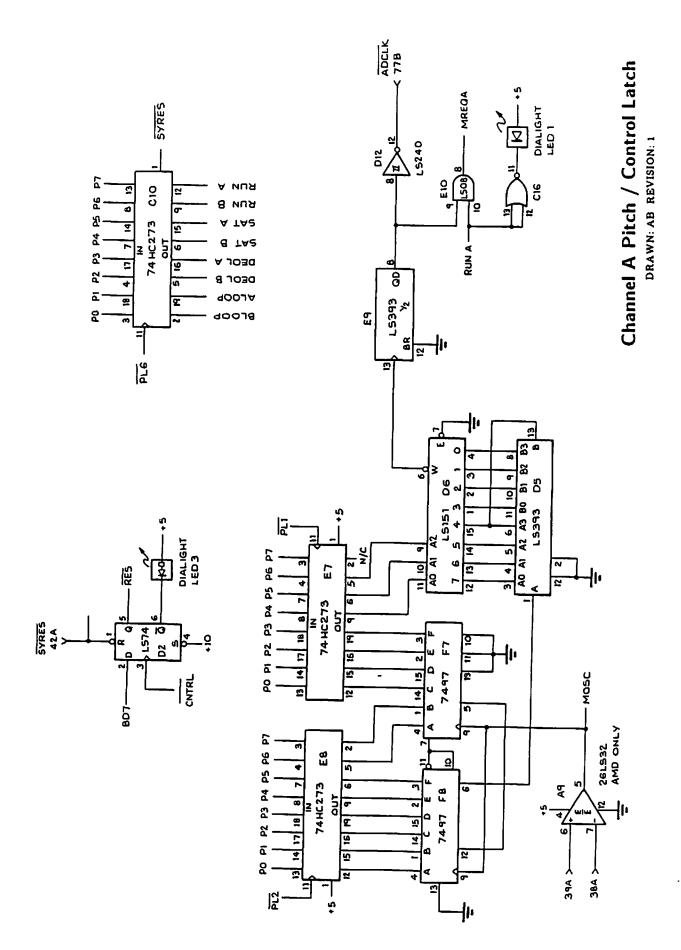

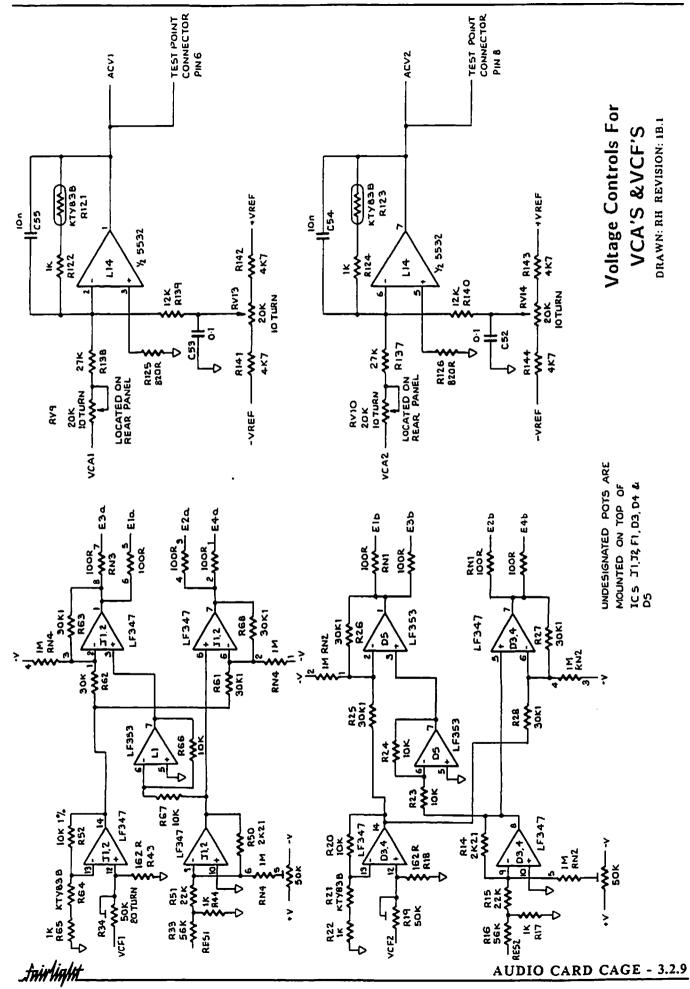

#### The channel cards

Each channel card contains a 2Mhz 6809 with 64 kbytes of program memory and the circuitry to generate 2 channels of wave form pitch, level, filter setting, resonance and address information. The channel cards themselves contain no waveform memory.

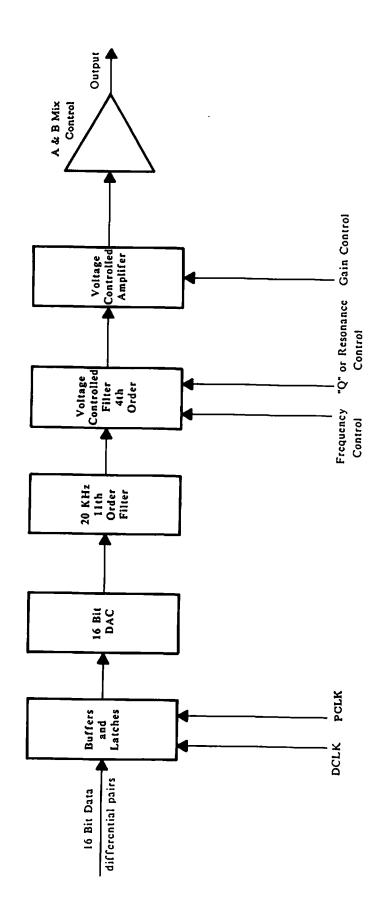

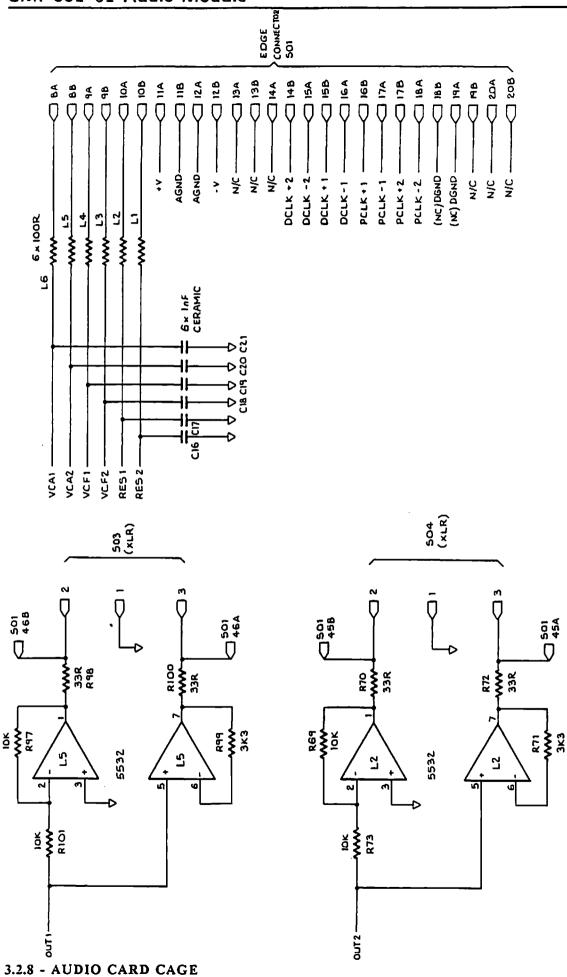

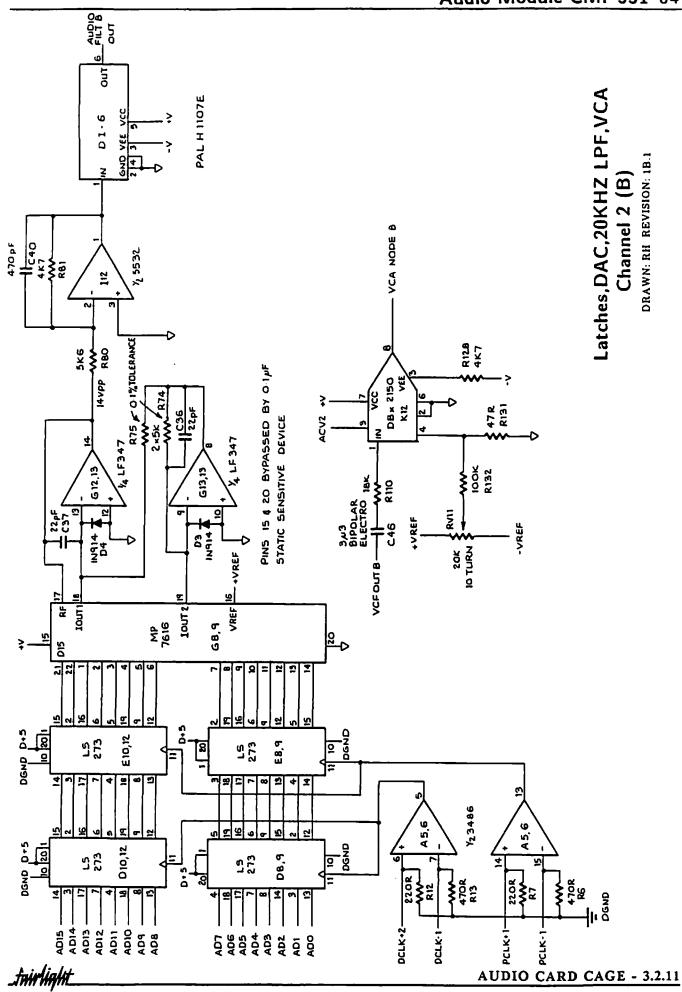

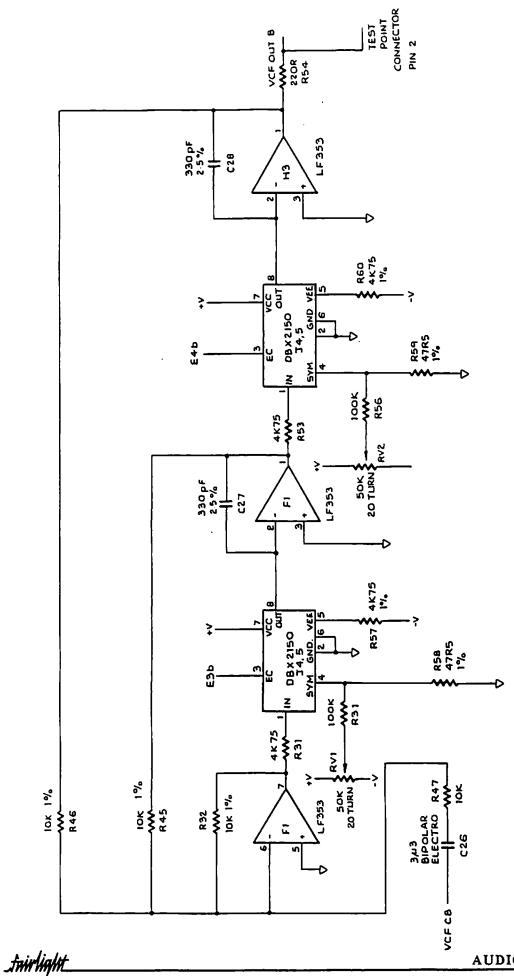

Access to the waveform RAM is via fixed cycling allocation. Each channel card is connected to one Audio Module by a 26-way flat cable which carries the control voltages, pitch and clock information used to clock the 16 bit DACs, and control the VCAs and VCFs.

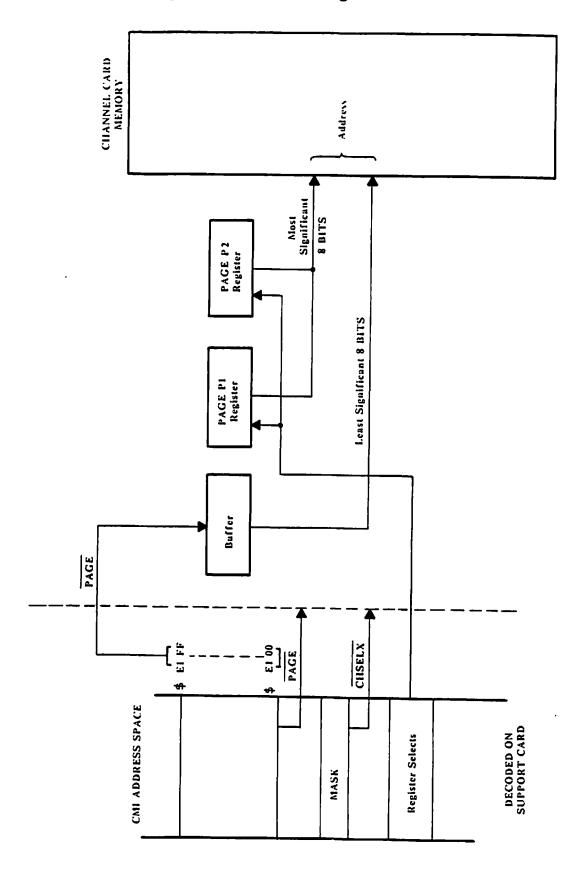

#### Channel Support Card

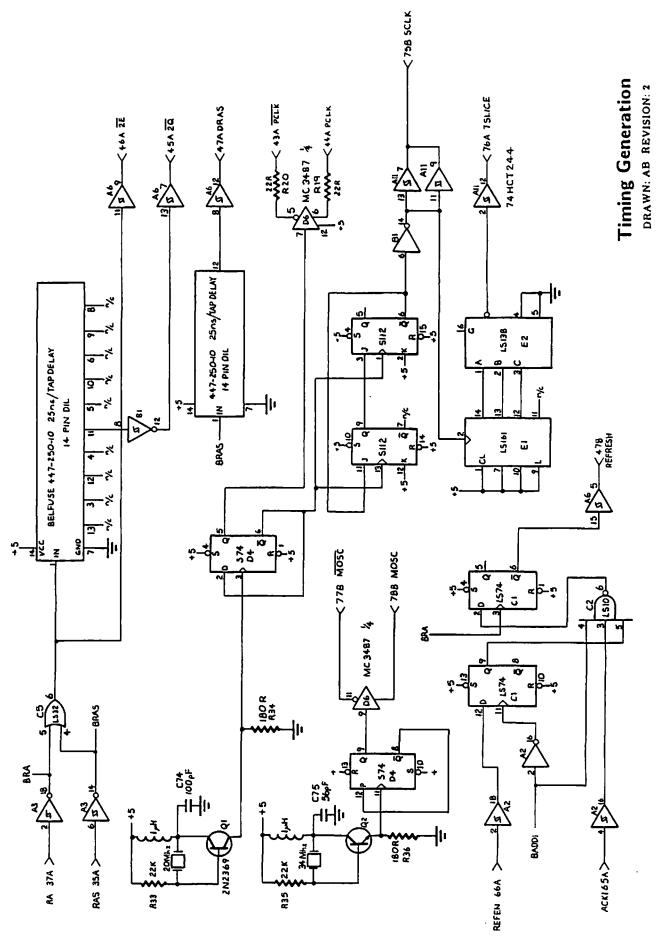

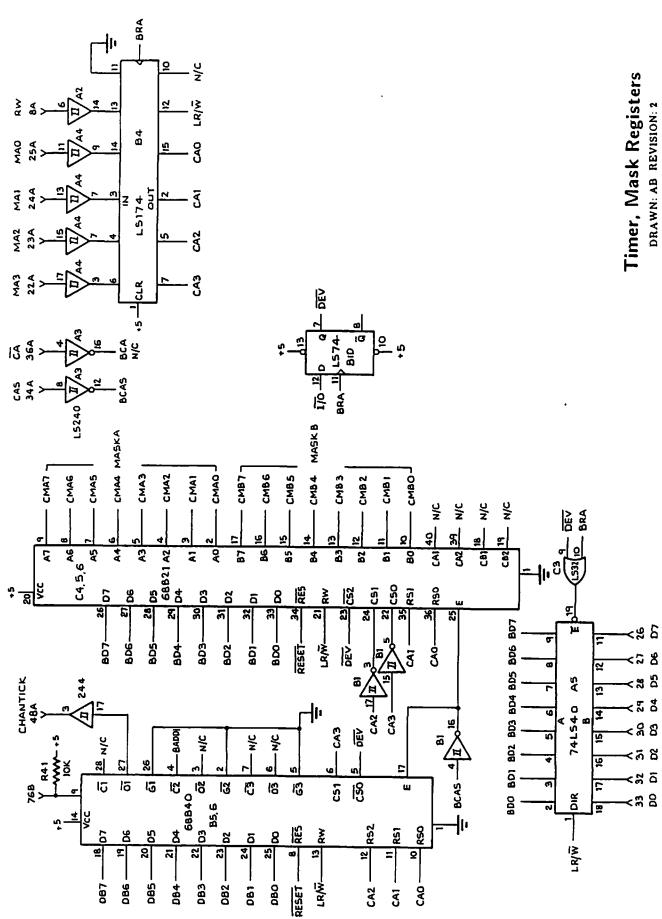

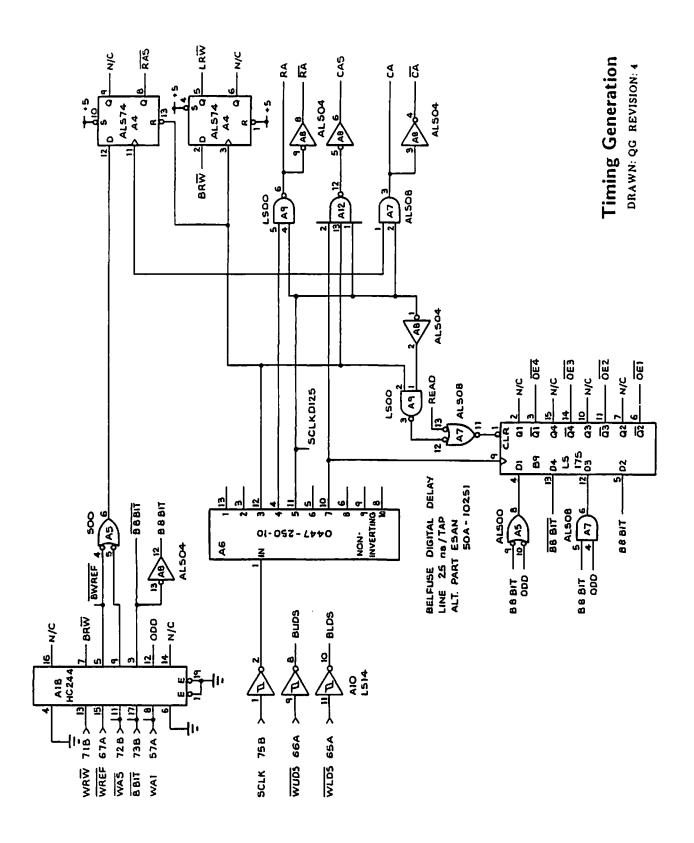

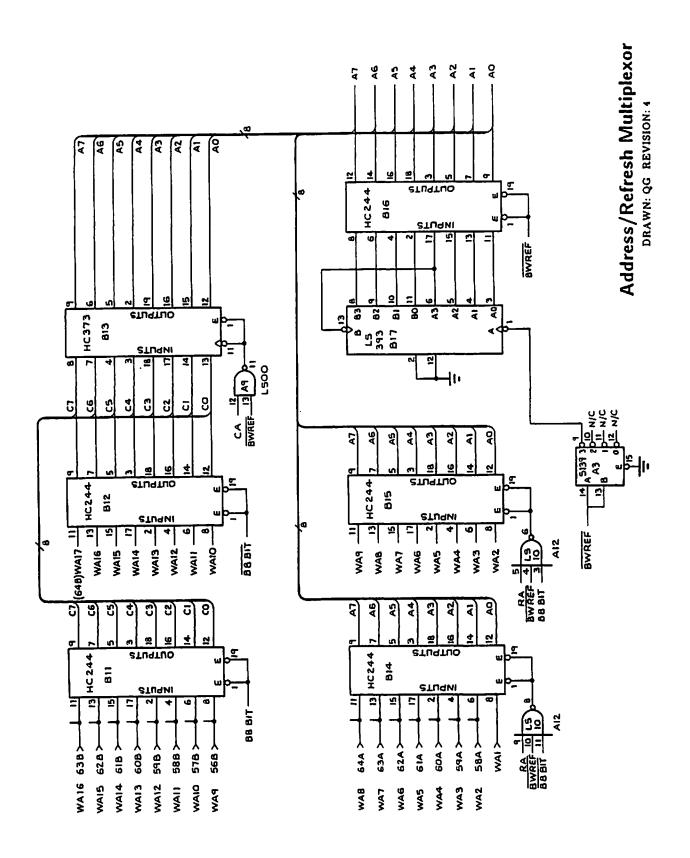

This contains the timing generation and time slice allocation logic for the channel cards and the waveform buss. It also contains the channel card addressing logic, channel masks, some channel card program RAM refresh logic and master pitch oscillator. The time slice logic generates 8 equal time slices that are subdivided internally to the channel cards, each channel card generates 2 channels 8 time slices apart.

e.g. channel card 1 generates channels 0 and 8, channel card 2 generates 1 and 9 etc.

The Channel Support card also contains a timer which has one output bussed to all channel cards where it will cause FIRQs (Fast Interrupt Requests). This real time clock is used for channel card envelope timing.

#### Waveform Processor

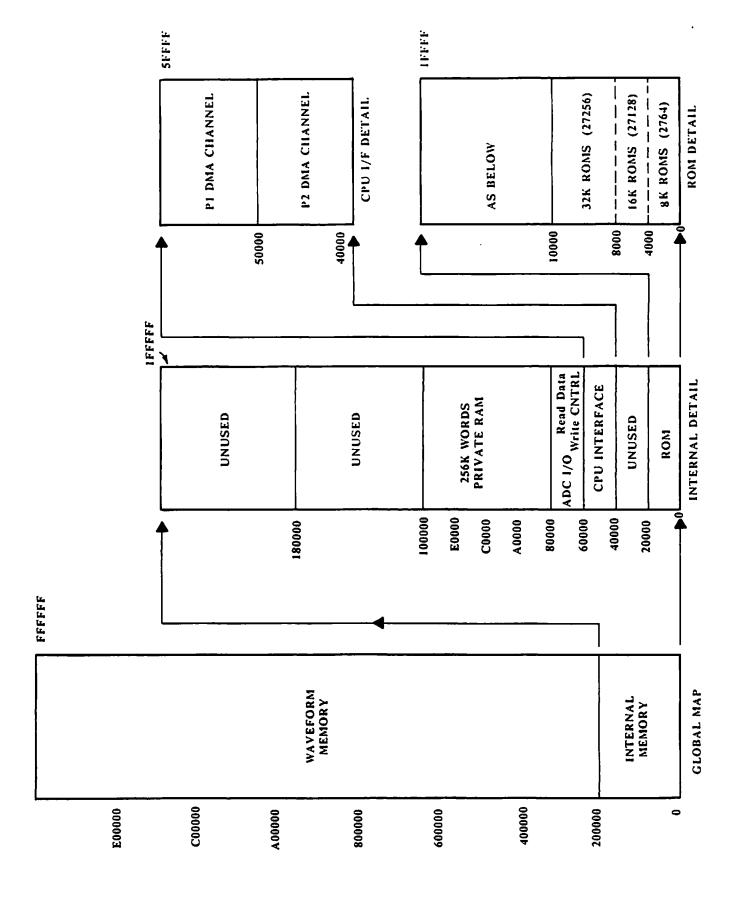

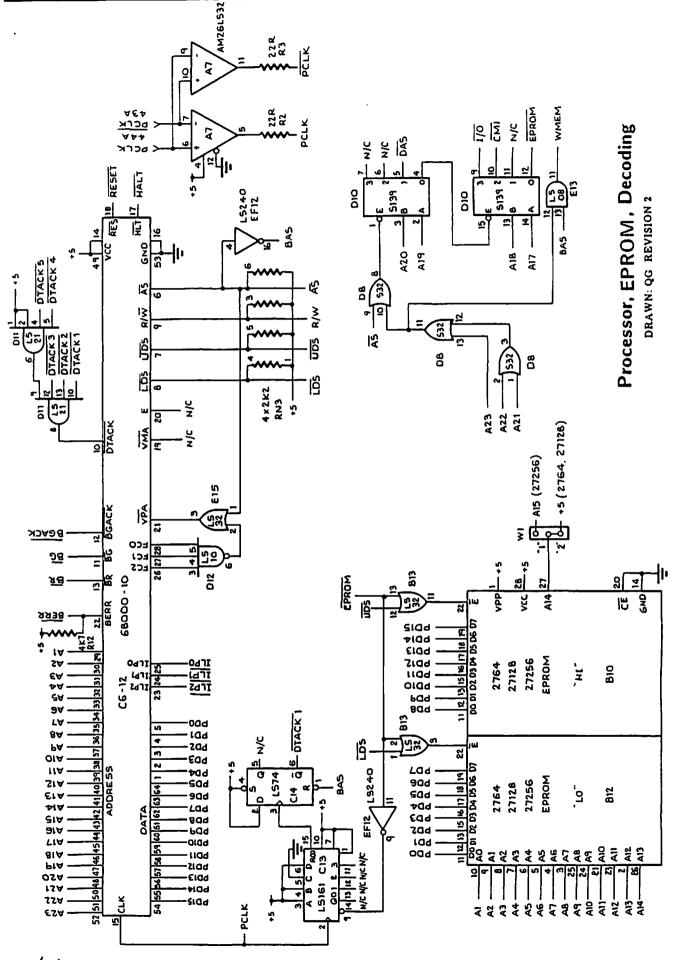

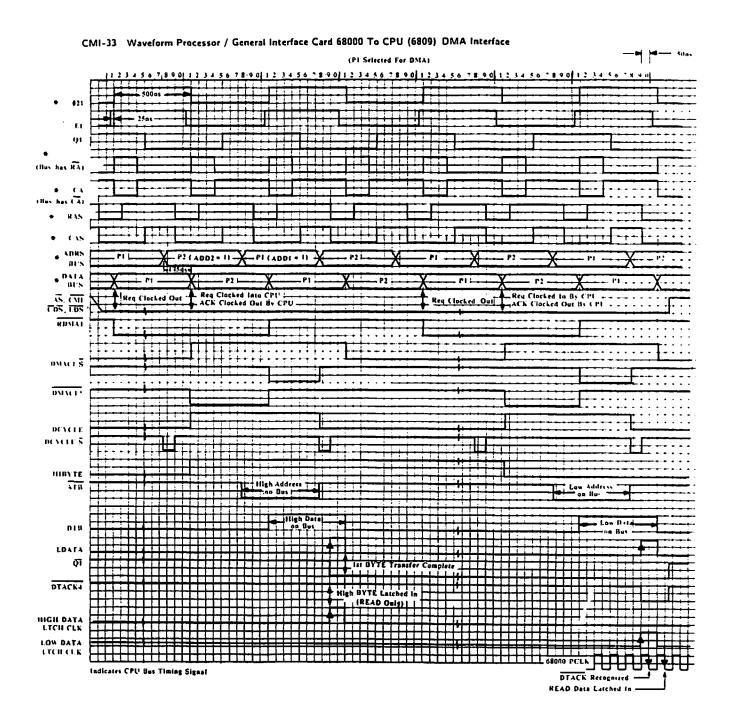

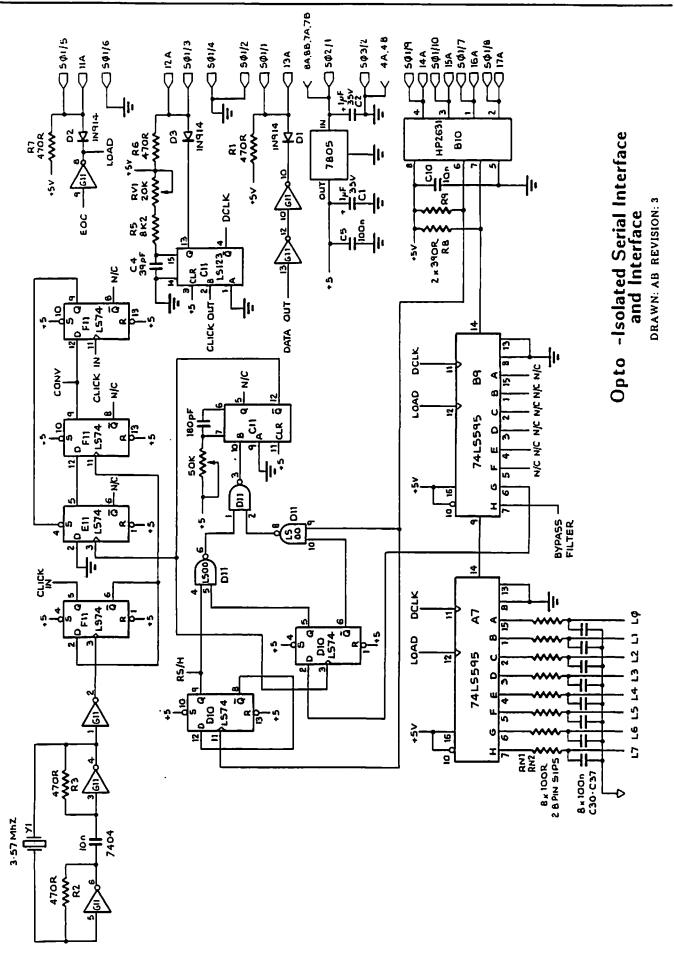

This is a 10MHz 68000 with 8k words of ROM, 256k words of RAM, optically isolated serial interface to the ADC module, a waveform buss interface and a CPU buss interface. It also contains the Waveform Ram refresh arbitration logic. Access to waveform RAM is allowed during unused channel card time slices. 68000 code can run in waveform RAM if required.

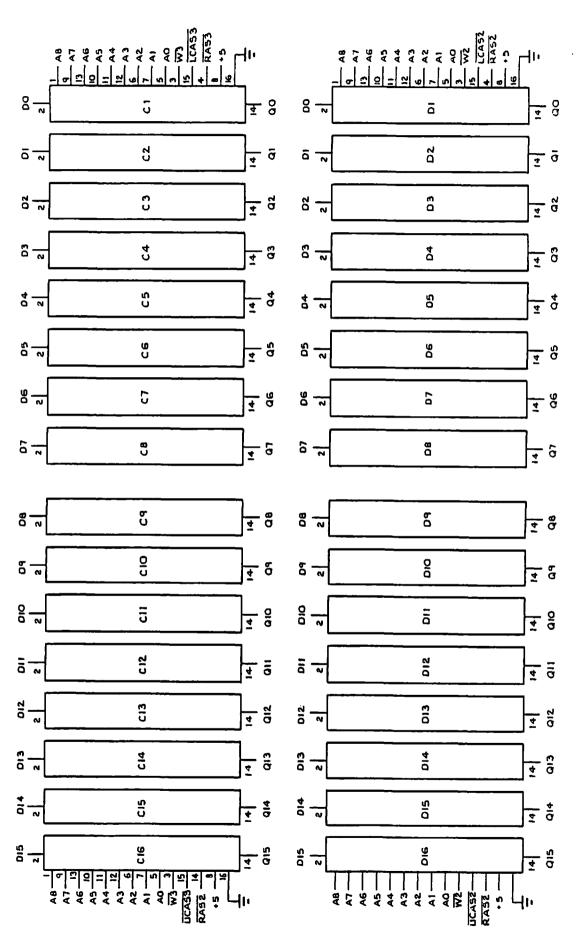

#### Waveform RAM

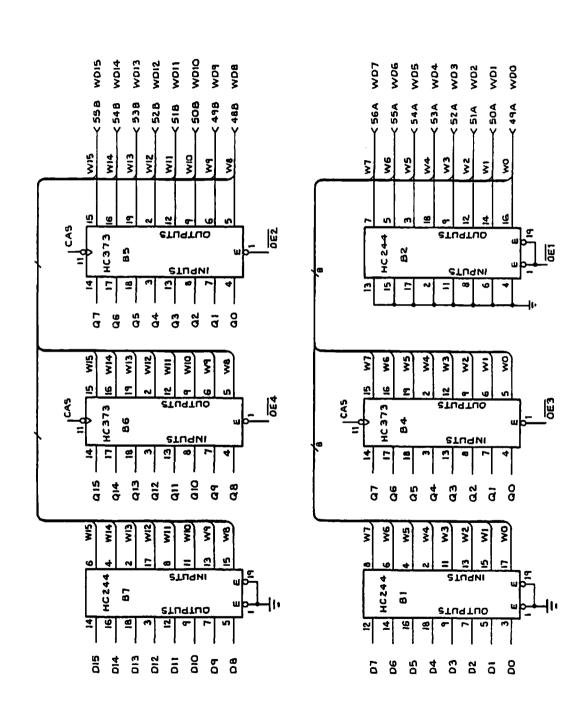

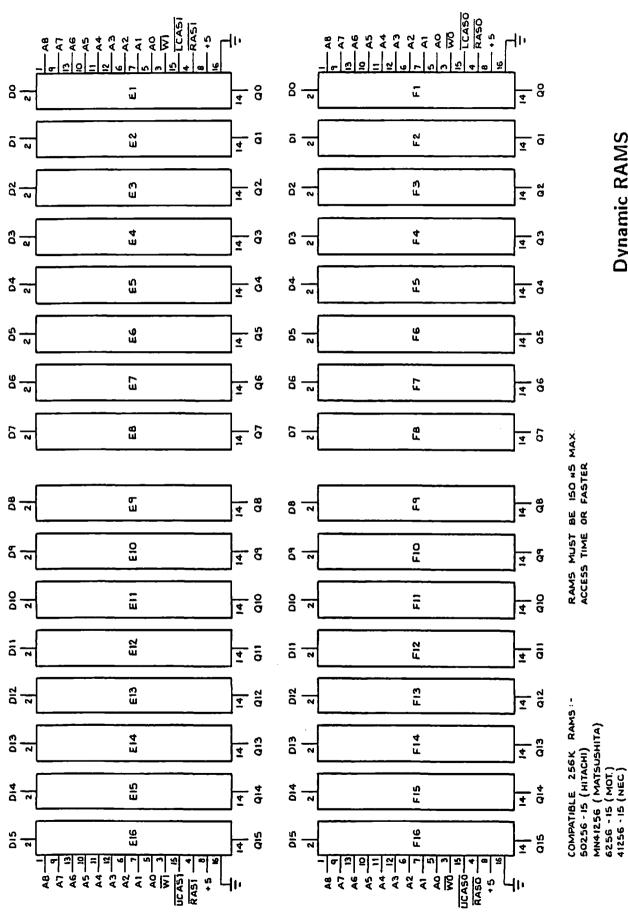

Each Waveform RAM card contains 1M words of 16 bit waveform RAM. This RAM is refreshed by an on-board counter and logic on the Waveform Processor. Refresh cycles are only granted if no channel accesses are requested. An 8-bit mode is also supported for doubling sample time on low resolution samples.

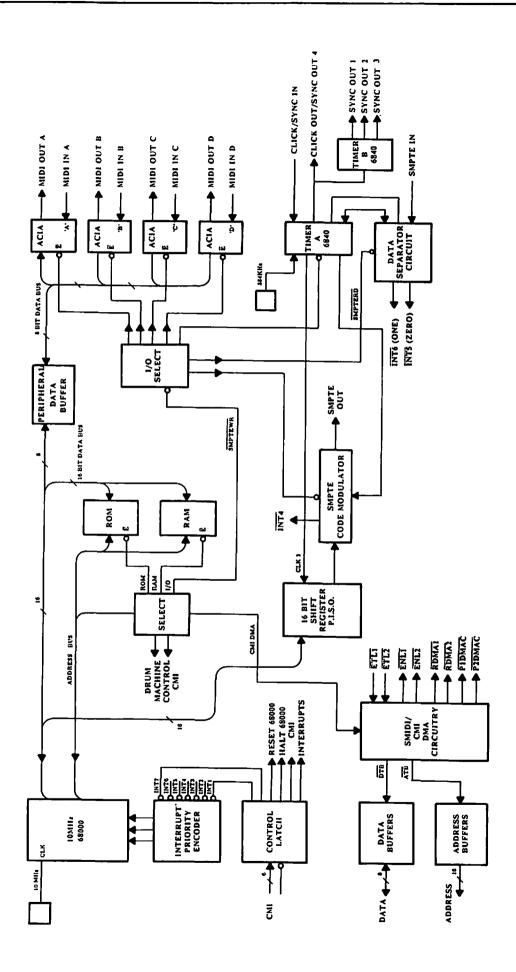

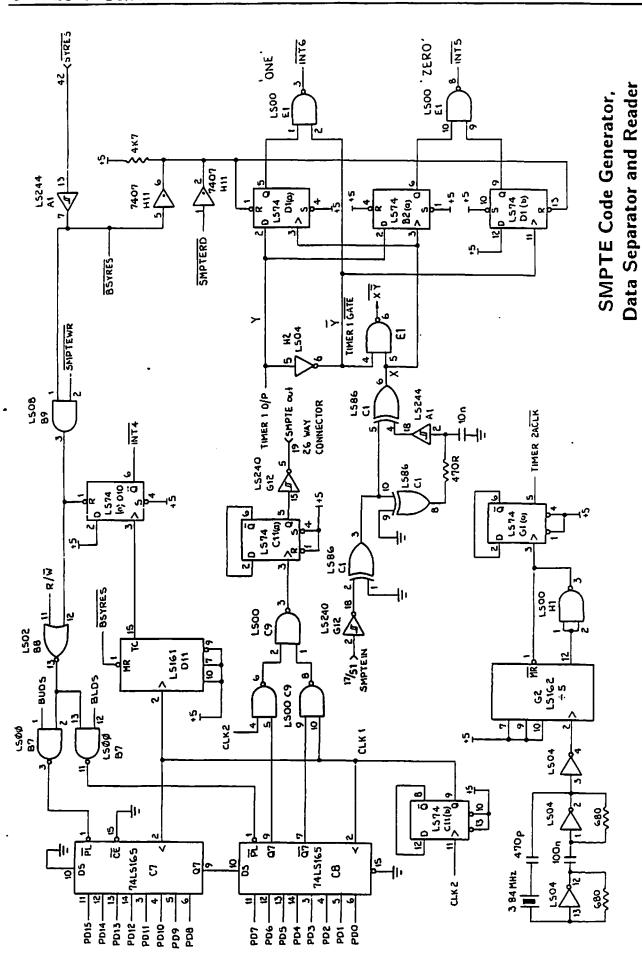

#### General Interface Card

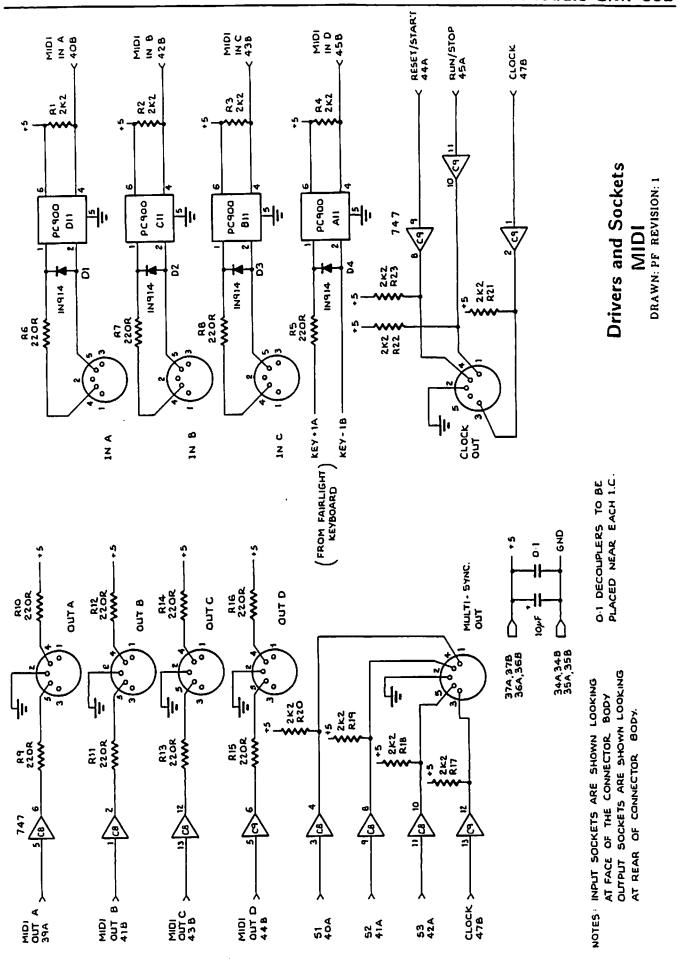

This board contains 4 MIDI in/out channels, SMPTE in/out, and synchronization clocks and clicks for the world beyond Fairlight. The music keyboard connects to this via one of the MIDI input channels. A 10MHz 68000 processor unscrambles control frames from key depresses and sends commands directly to the channel cards to play without intervention from the CPU. This processor also plays a major role in running music sequencers.

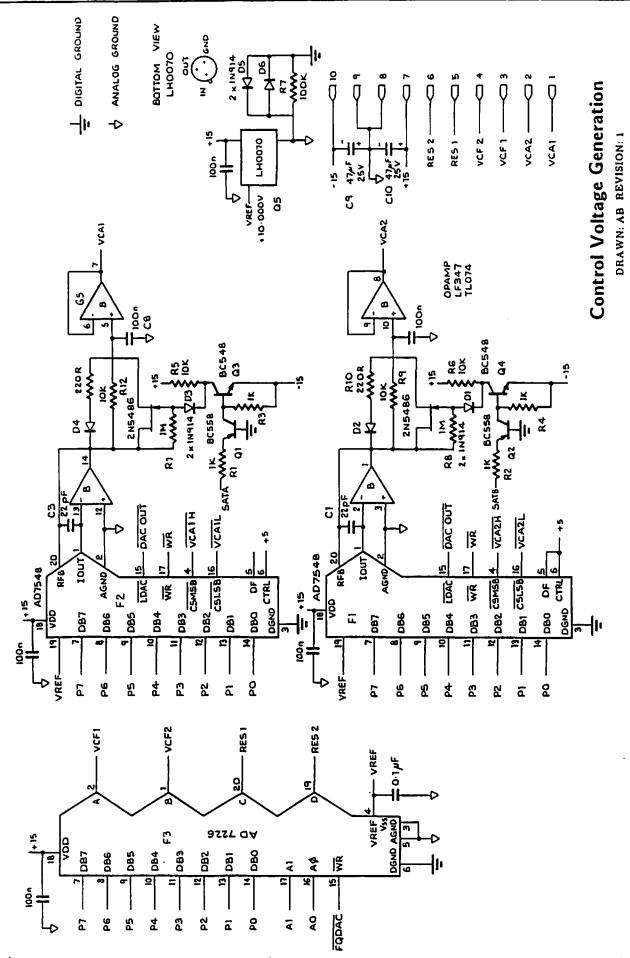

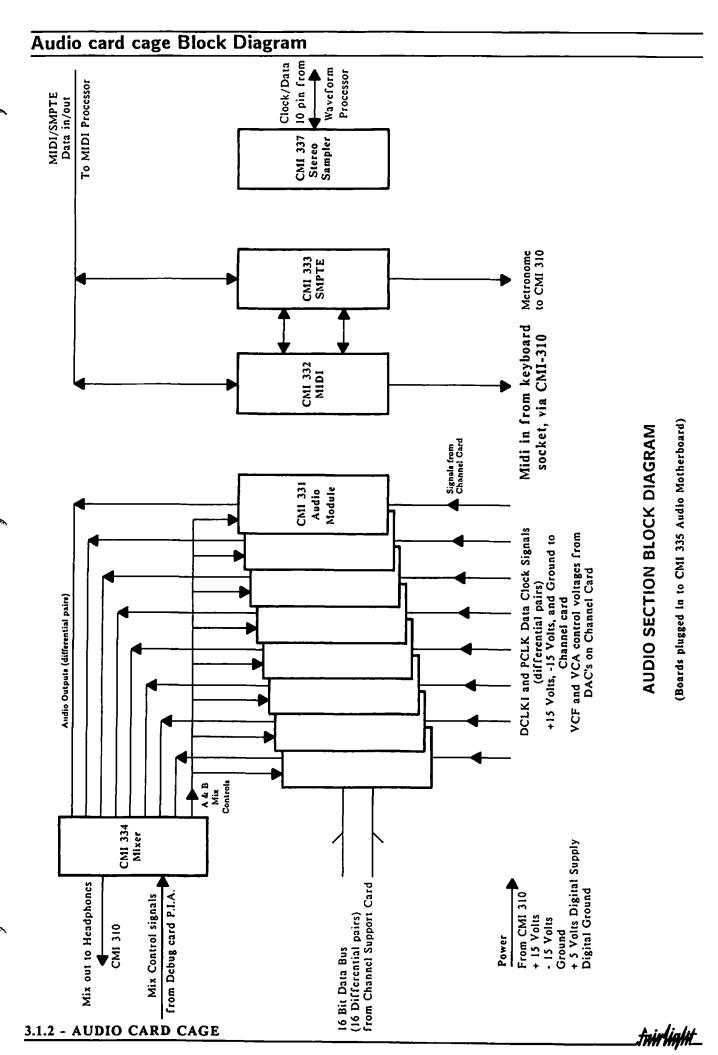

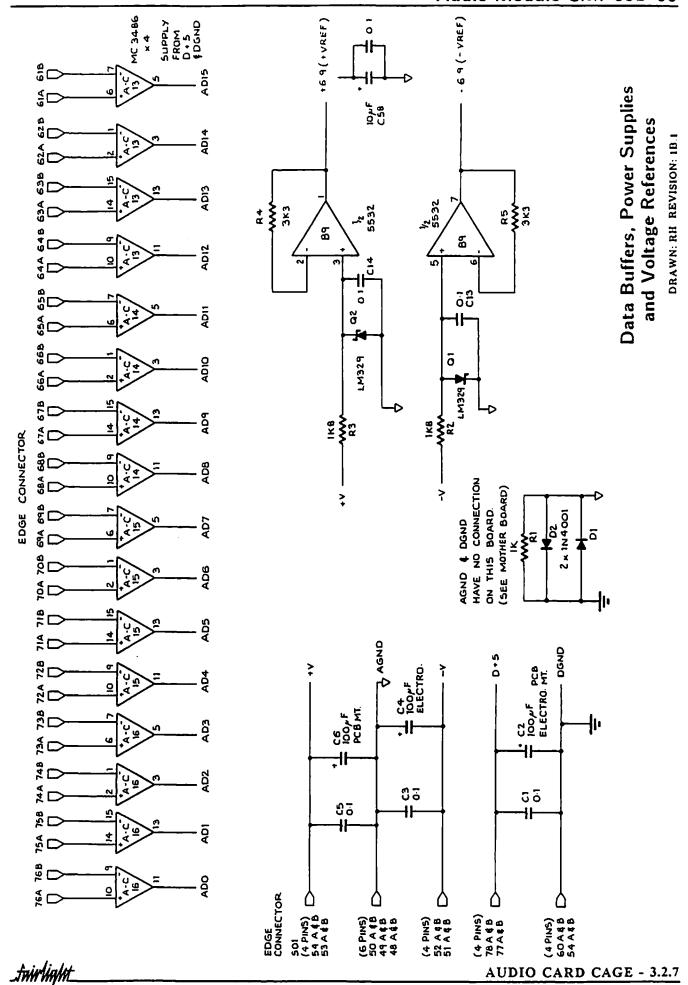

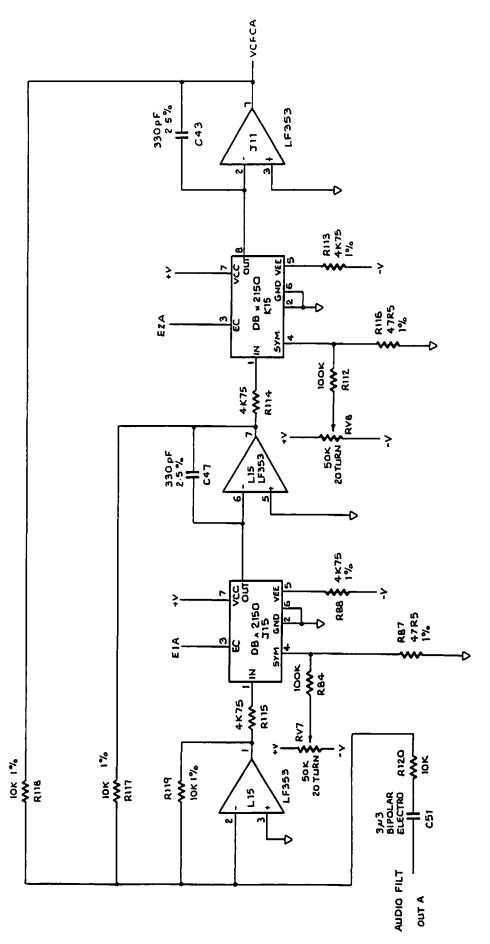

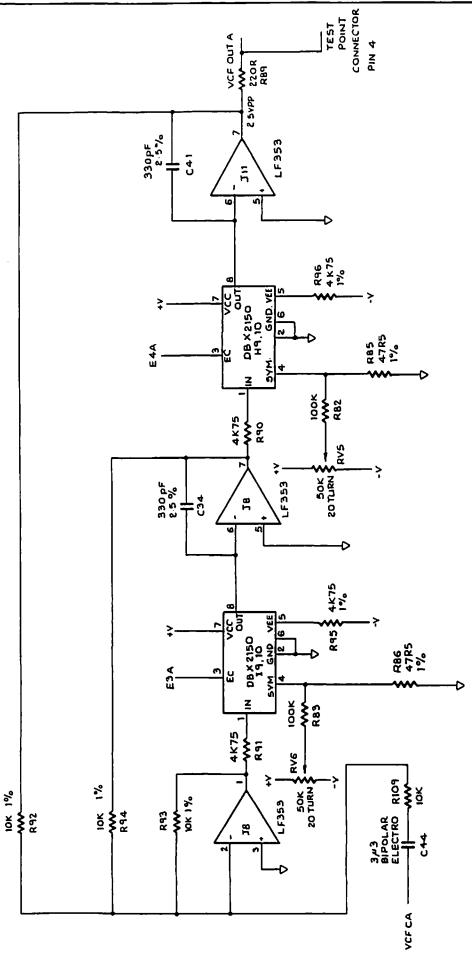

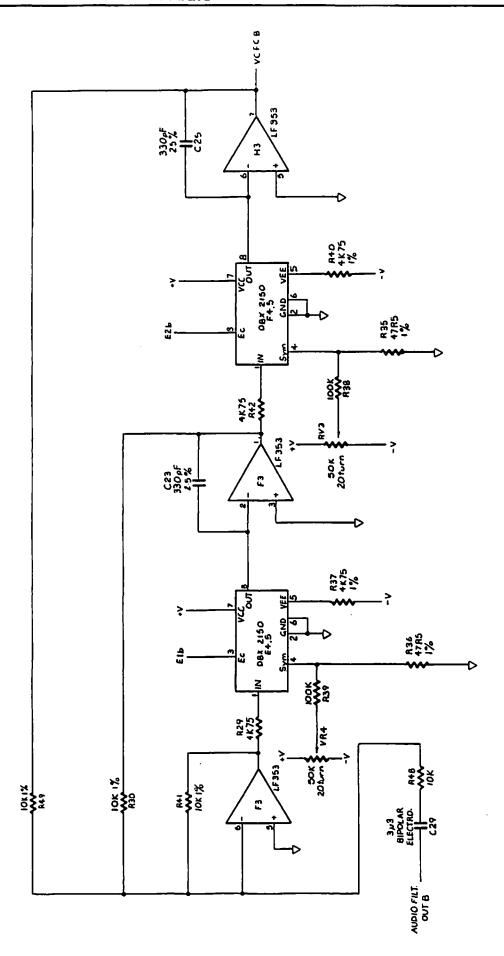

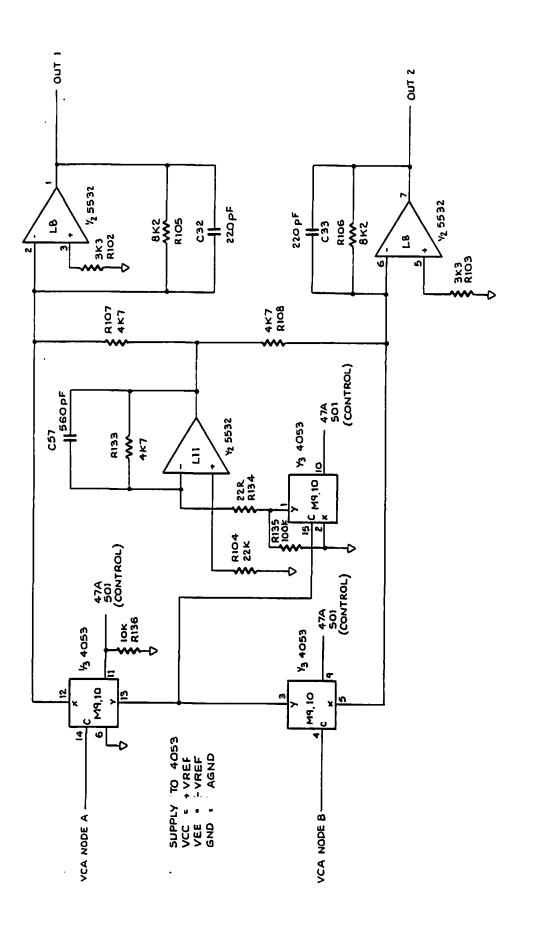

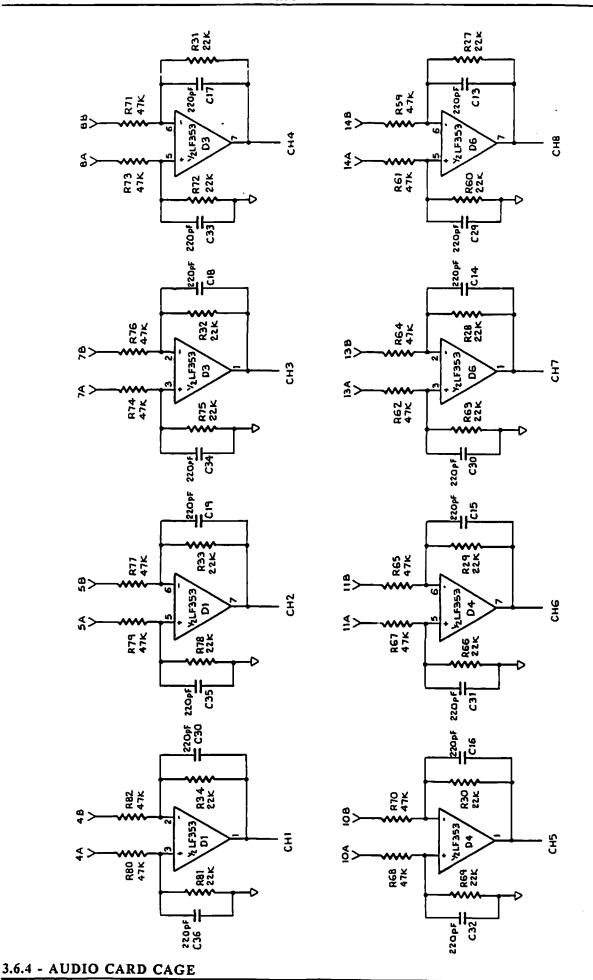

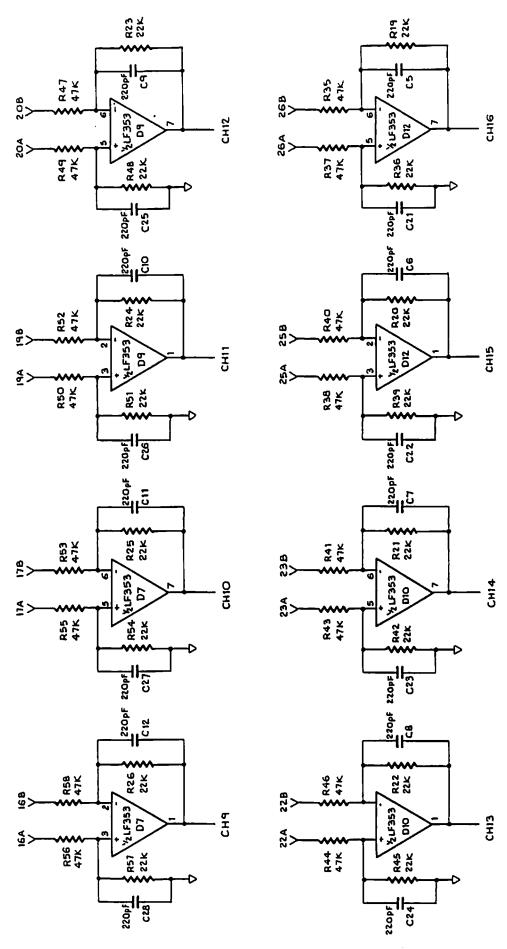

#### Audio Output Modules

These plug into the Audio Motherboard from the rear of the CMI Mainframe. Each contains 2 channels of 16 bit DAC, voltage controlled filter and voltage controlled amplifier and line driver. The waveform data come via a single flat cable from the Channel Support card to the Audio Motherboard then along the audio buss to each of the Audio Modules. Control clocks and voltages come directly from the channel cards via individual flat cables terminated in PC-mounting sockets on the Audio Motherboard. A switchable mix facility allows the two channels on each Audio module to be mixed.

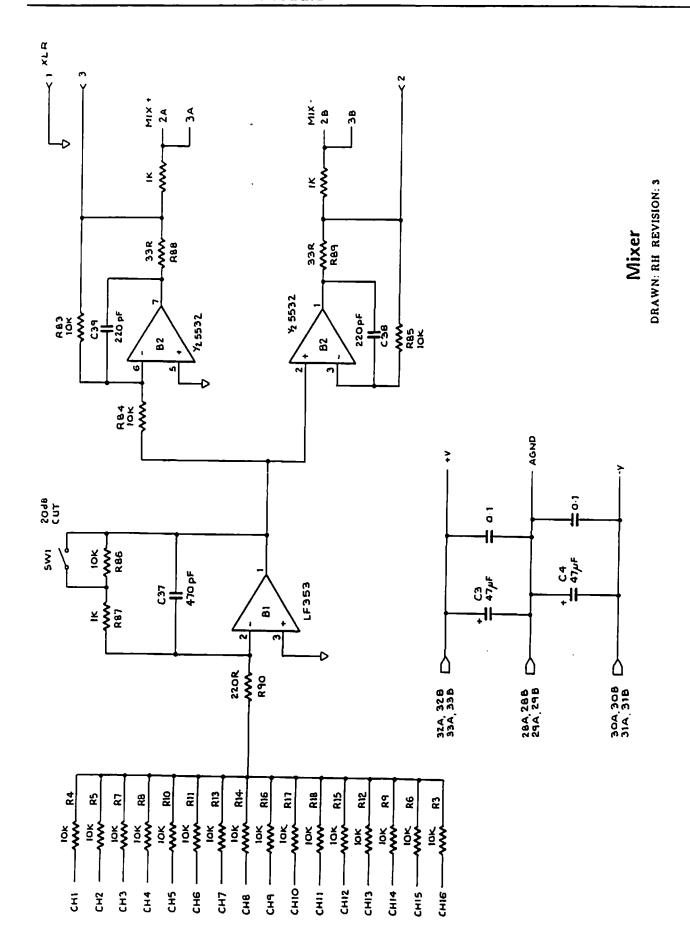

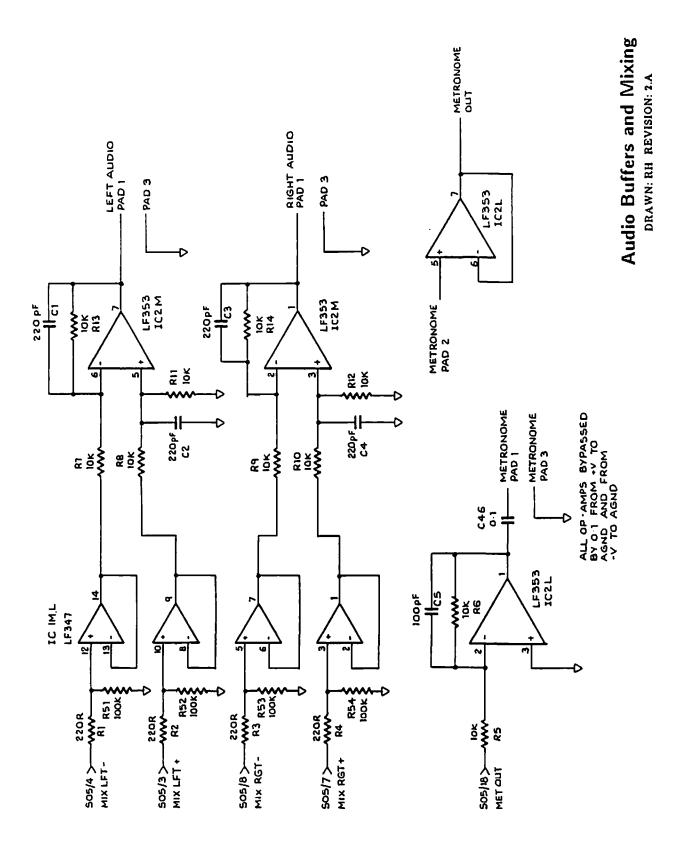

#### Audio Mixer Module

The Mixer plugs into the Audio Motherboard from the rear of the CMI Mainframe and provides a single equally mixed output of all 16 channels to both a line socket and the headphone amplifier.

#### MIDI Support and SMPTE Support Modules

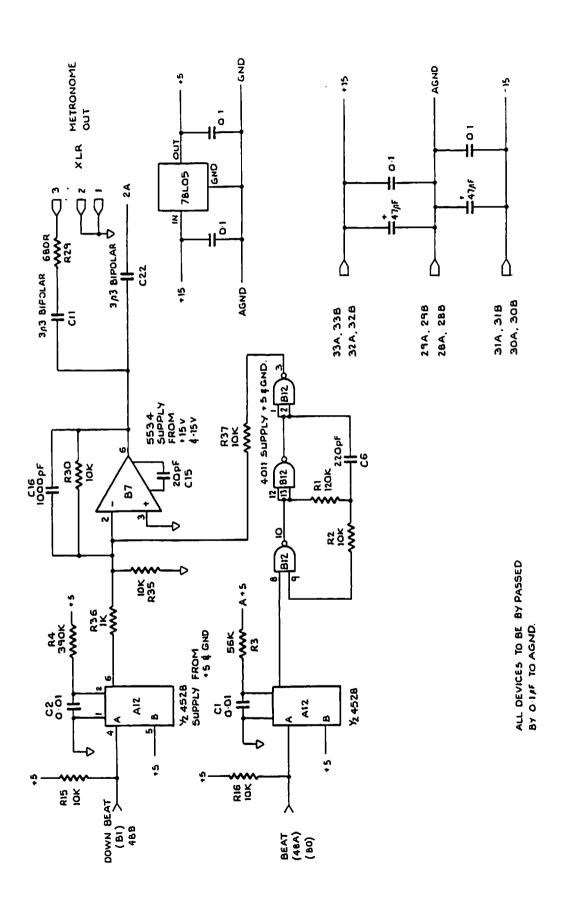

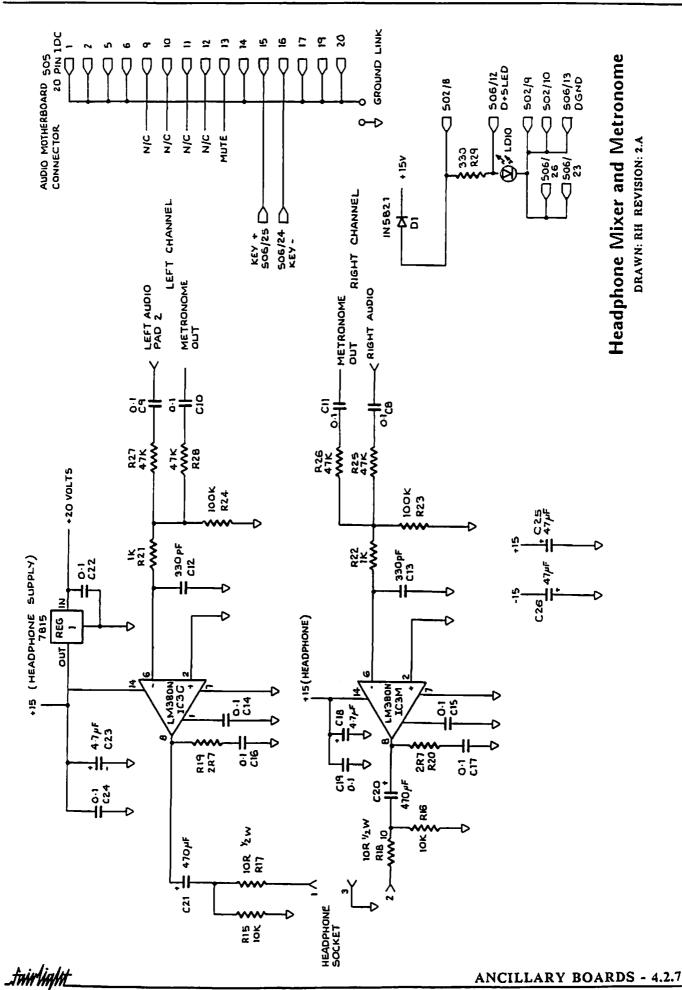

Both these modules plug into the Audio Motherboard from the rear of the machine. The SMPTE support module contains the analogue I/O circuitry required for SMPTE time code plus an electronic metronome which is controlled by data from the PIA output of the CPU Control Module and whose output is mixed onto the headphone amplifier.

The MIDI support module contains the optical isolation circuitry required for MIDI and provides mounting for the 5pin DIN connectors. Connections from both modules go to a socket on the Audio Motherboard which receives the flat cable connected at the other end to the General Interface Card.

#### Hardware/Software Relationships

This section gives a summary of the operational concepts involved in each of the CMI's major functions. This information should help relate a particular software function to the appropriate piece of hardware.

\_tairlight\_

The software system is divided into two main sections, the resident software and overlays. The resident part is responsible for all the real-time functions such as sound generation, keyboard input processing and graphics pad operation. The overlays are used for the various control and sound manipulation functions provided by the display pages. Changing pages on the CMI loads a new overlay for that page from disk. Some pages use further overlays themselves, so that when certain functions are invoked from a particular page for the first time, a disk access will be made as the overlay is loaded.

Both 6809 processors access 65K bytes of program RAM, switched from the 256K memory board, so that some of the code may be executed by each processor individually, and both processors can share common data structures. Processor 2 carries out the non real-time functions such as disk I/O and graphics display.

The 68000 Waveform Processor is concerned with movement of data into and out of waveform memory and manipulation of data in waveform memory.

The 68000 MIDI Processor is concerned with starting and stopping

A broad description of a range of specified functions follows.

#### \*\*\*\*\*System Startup/Boot

When power is first applied to the system, a power-on reset signal is am generated for about a half second by a timer located on the Processor Control card, Q133. At the end of this time, both processors fetch increstart vectors from EPROMS, also on the Q133 card and start executing the startup procedure in EPROM. Processor I initialises all the registers of the peripheral controller devices such as PIAs and Processor 2 initialises the Graphics Display, clears the ... screen, loads disk driver firmware into system RAM from ROMs on the QFC - 9 and/or Q - 777 controller modules, and displays the LOAD SYSTEM DISK IN DRIVE greeting. While this is happening the processor internal to the Music keyboard also starts up. The Music keyboard LED display first diplays the message POWER ON, and then the message SERIES III. Processor 1 then loops, waiting to be triggered by Processor 2, which in turn loops waiting for a disk to be inserted in drive 0, as indicated by the appropriate status bit from the Floppy-disk Controller Card OFC9.

When the system disk has been correctly inserted, processor 2 executes the first stage of the bootstrap loader firmware (located on the Q133 card). This involves reading in the boot block, which is a special sector on the system disk. The code stored in the boot block is then executed which completes the boot load by loading the operating system and the Page I overlay. When Page I starts up, the message PAGE 1 READY is sent to the music keyboard display.

#### Disk Operations

. .

The CMI uses one eight-inch double-sided floppy disk drive and one or two 5.25" hard disc drives.

#### Floppy disk

Floppy disk format is soft sectored, 128 bytes per sector (single density), or 256 bytes per sector (double density). FM recording is used for extra reliability. The floppy drive itself is controlled by a Western Digital WD1791 L.S.I. controller located on the Floppy Disk Controller Card QFC9.

The Floppy disk driver EPROM is located on the QFC9 card. Routines in this EPROM provides utilities including read sector, write sector, and verify C.R.C. which are called by the RAM-resident disk-operating system.

In the event of a disk error being detected during a read or write operation, the software will perform a number of re-tries, including head relocation, to try to recover from the error. If the error persists, an error message is displayed.

#### Hard disk

The hard disk is controlled by the Q777 SCSI TSmall Computer Systems Interface) card. The hard disk driver firmware is located on the Q777 card. Hard disks are 85 Meabyte or 140 Megabyte, expandable as required.

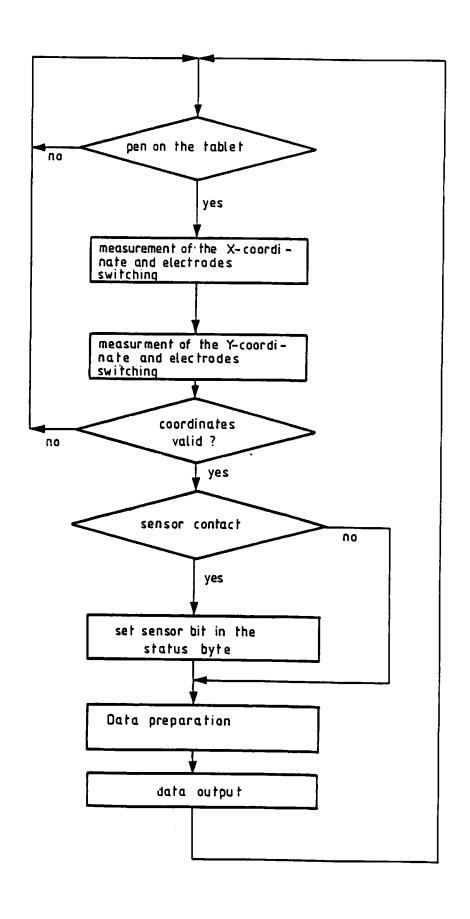

#### Graphics Display, Graphics Pad

The graphics display is generated by writing a bit-mapped image to the dedicated 16K byte VRAM. This block of RAM is mapped in and out of the processor memory space under software control. The graphics pad sends special format ASCII characters through the same path as normal ASCII characters from the alphanumeric keyboard. These are then converted into graphics coordinates, and VRAM addresses, in software, which also generates the graphics pad cursor.

#### Command entry

Data arriving from the alpanumeric keyboard is fed to the ACIA on the Q133 Processor control card. Alphanumeric characters are passed to Processor P2. They are then processed by the OS9 Operating System.

#### Loading/Saving Sounds

Sounds are stored on hard disk. Each voice file occupies up to 14 megabytes of disk space. The Voice files and other user files are stored in the directory /CMIF/CMIFILES. When a file is loaded, the directory is searched and the address of the file found. The Voice is then DMA'd into the system memory under the control of Processor 2, and DMA'd from the system memory through to the waveform buss via the waveform processor. Saving sounds to disk operates by the reverse process.

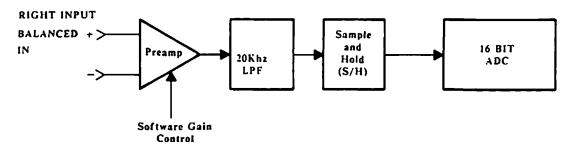

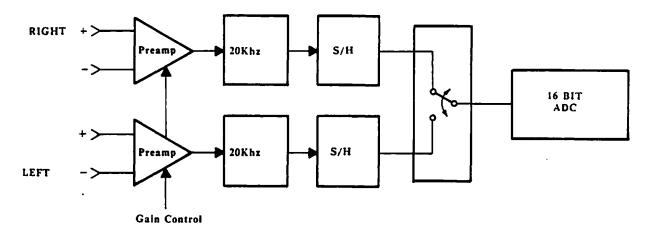

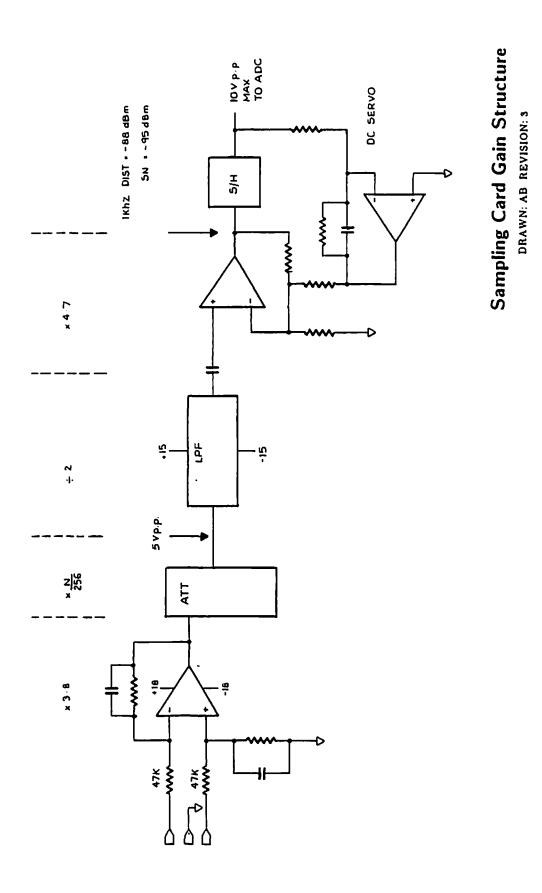

#### Sound Sampling

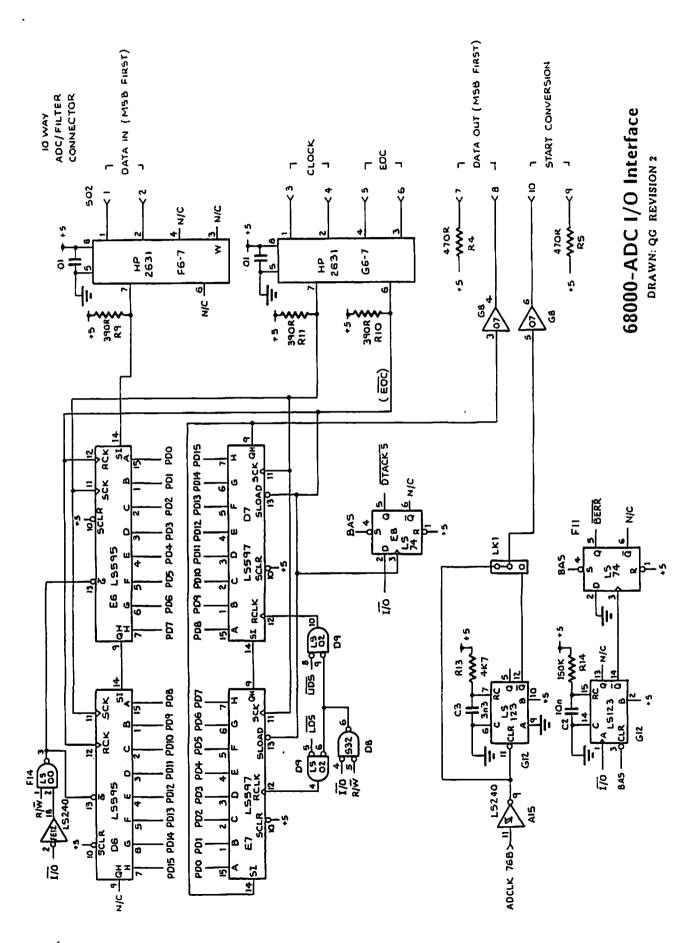

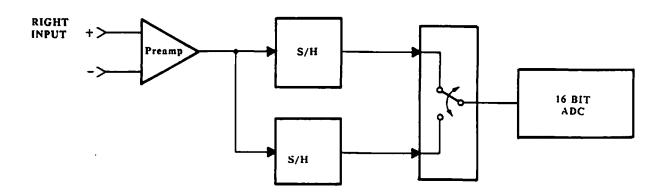

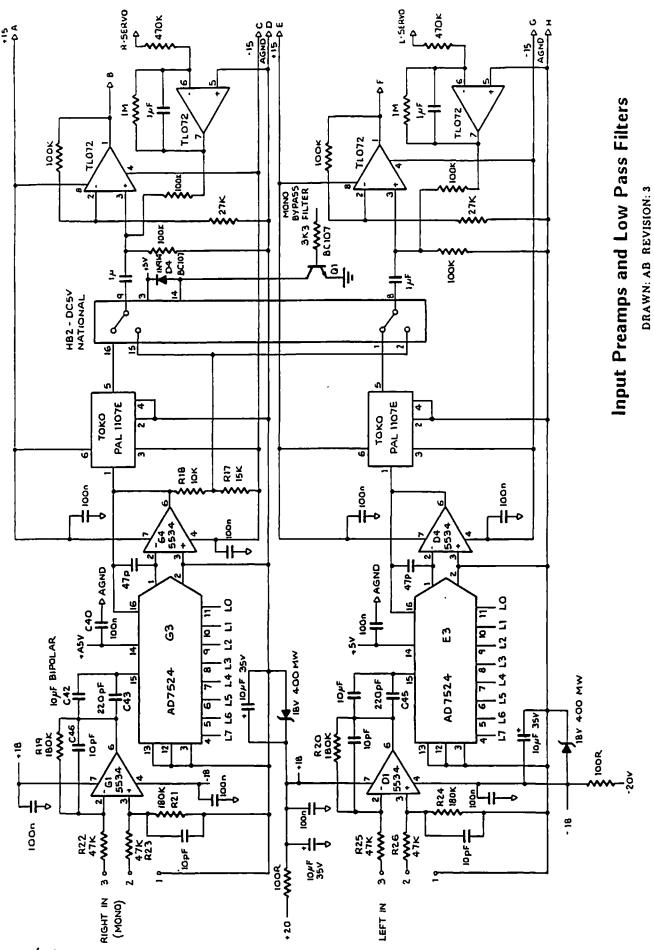

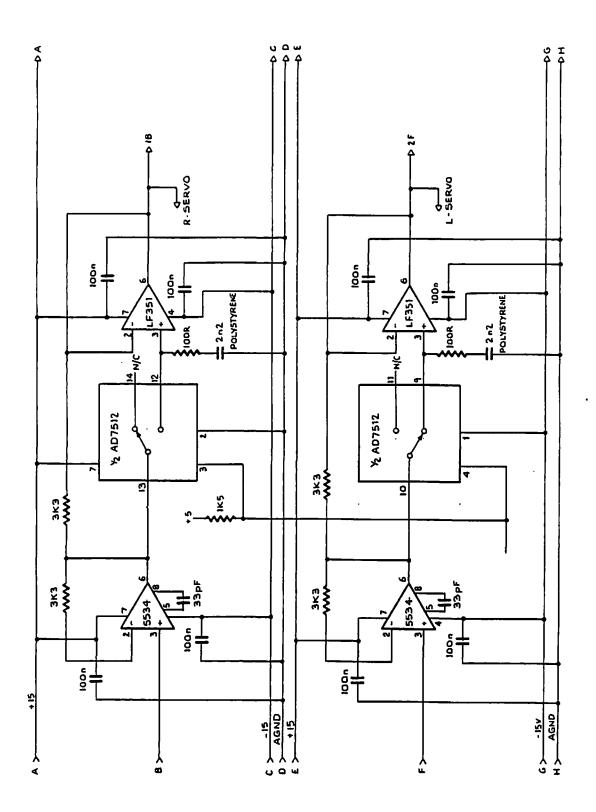

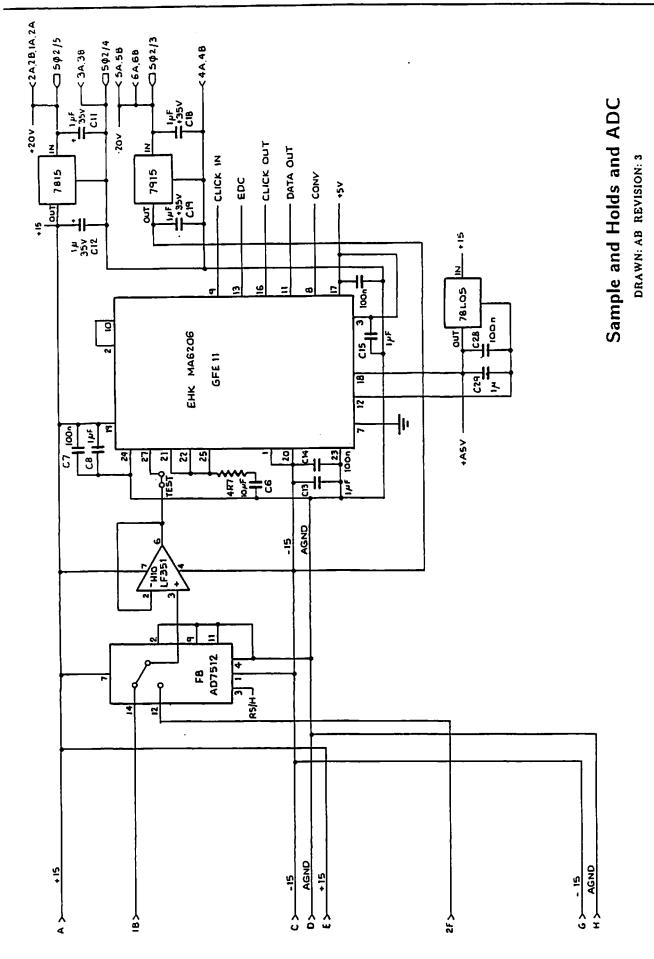

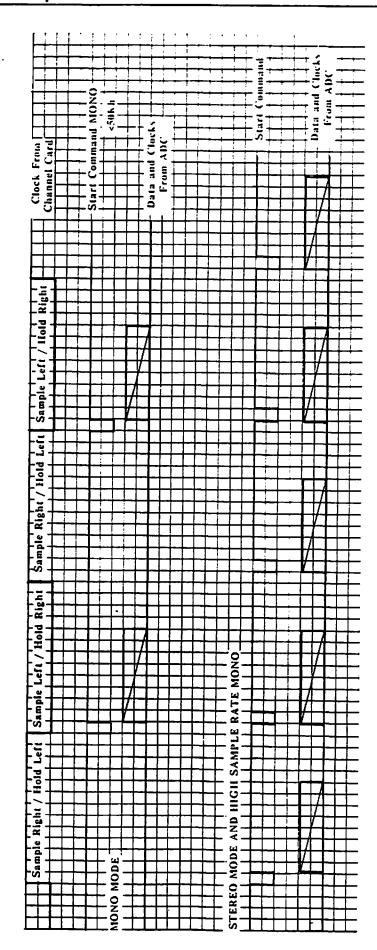

Audio input for sampling is fed to either or both of the Right and Left Line Inputs at the rear of the CMI III. The CMI - 337 Sample card performs the analogue to digital conversion. There is a single analogue to digital conversion circuit, which switches between left and right channels during stereo conversions. The sampling rate is a

\_tairlight\_

maximum of 100KHz in mono mode and 50 kHz in stereo mode. The sample rate is governed by the frequency of a pulse stream coming from the Channel Card in channel one position. The sample rate is therefore established by software which sets up channel one to operate at the sampling frequency specified on the Sample Page.

As each digital conversion is made, the digital sample is passed serially to the waveform processor via a 10 way cable, and thence to waveform memory. When the Sample command is issued, the waveform processor starts conversions and loops until the data read is of a greater absolute value than the number specified as Trigger Level. It then begins transferring data to the waveform RAM, until the number of samples made is equal to the number specified as Sample Number.

#### Playing Music from the Keyboard

Three byte MIDI frames are transmitted serially from the CMI music keyboard to the Port D ACIA on the CMI - 332 MIDI Support Module. At present Fairlight keyboard MIDI is confined to MIDI Channel 1. When other MIDI keyboards are used they can be configured to transmit through channels 1 to 16 of Ports A, B and C on the CMI - 332. MIDI frames then pass to the CMI - 28 General Interface card. The CMI - 28 is concerned with starting and stopping output channels. When MIDI data comes directly from the music keyboard, Processors 1 & 2 are not involved.

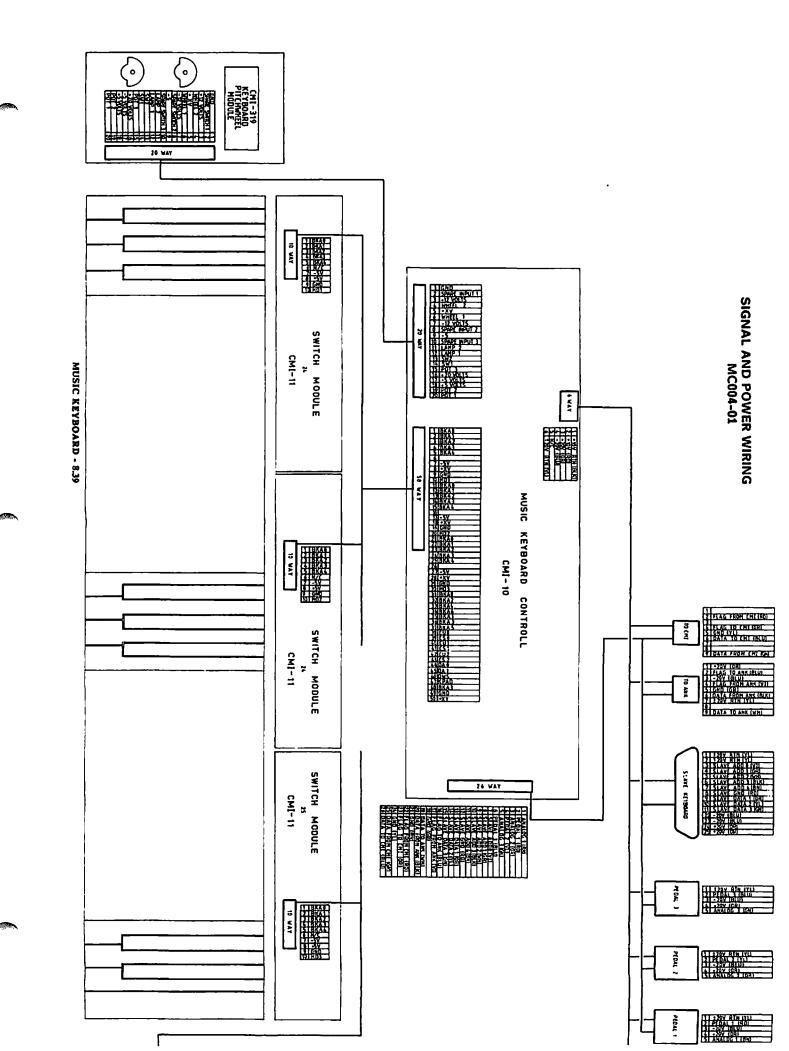

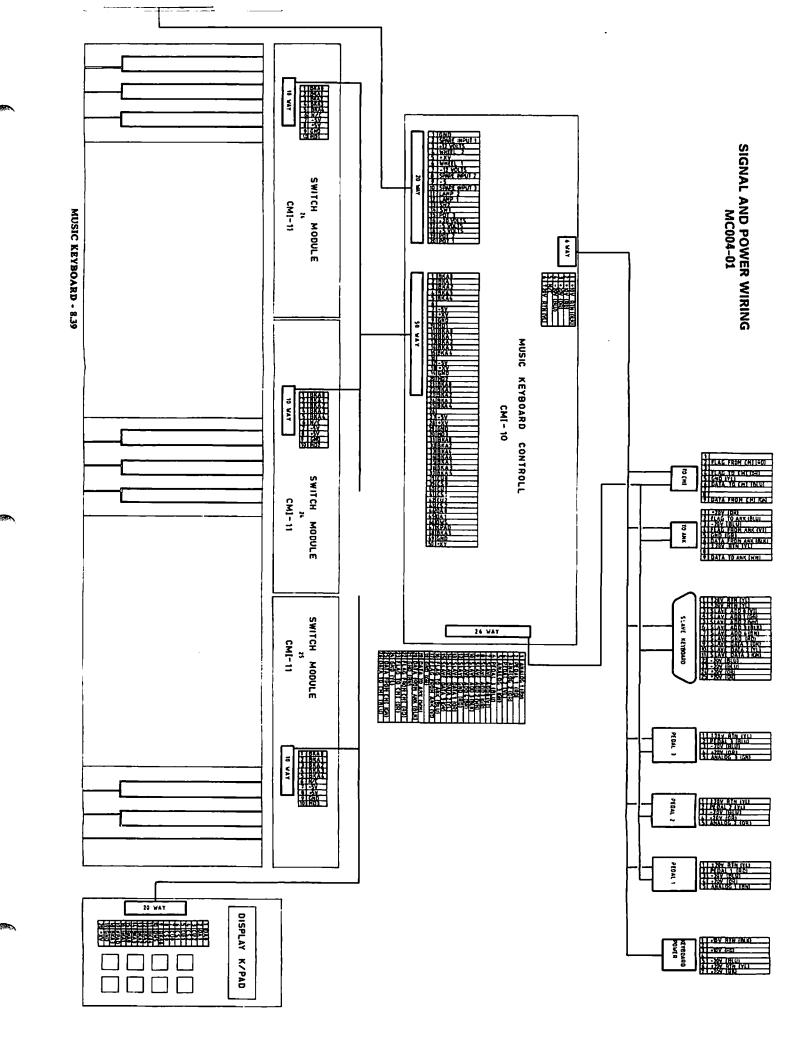

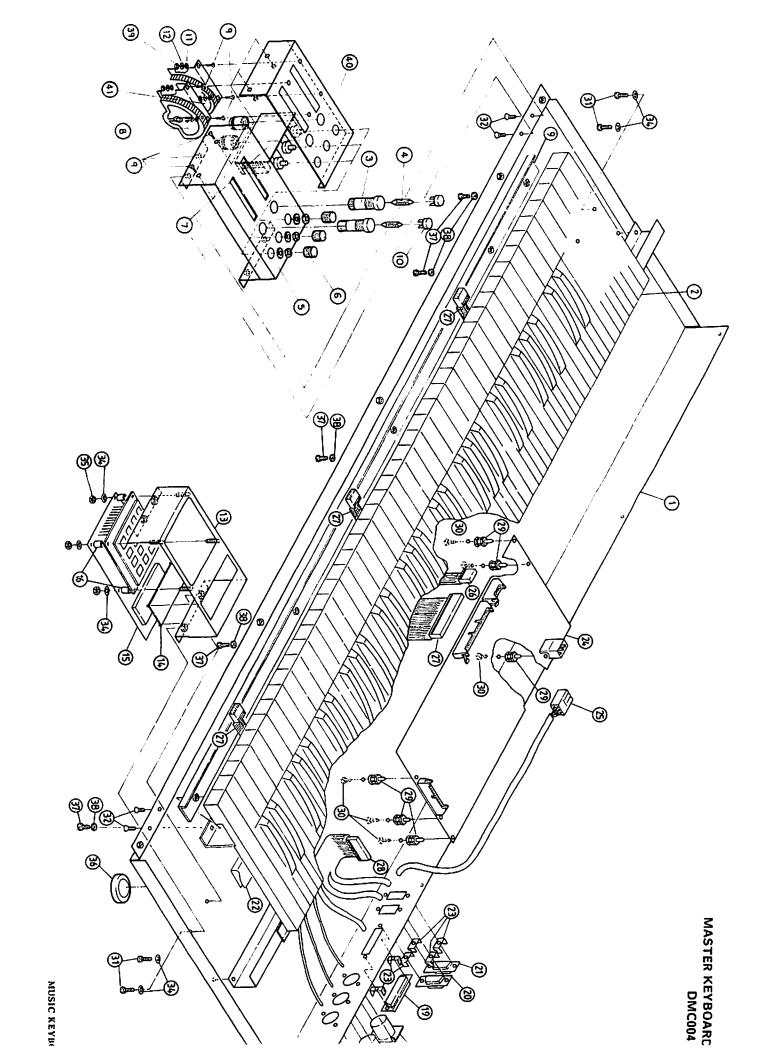

#### Music Keyboard Functions

As well as sending music key depression/release data to the mainframe, the music keyboard has a number of ancillary functions.

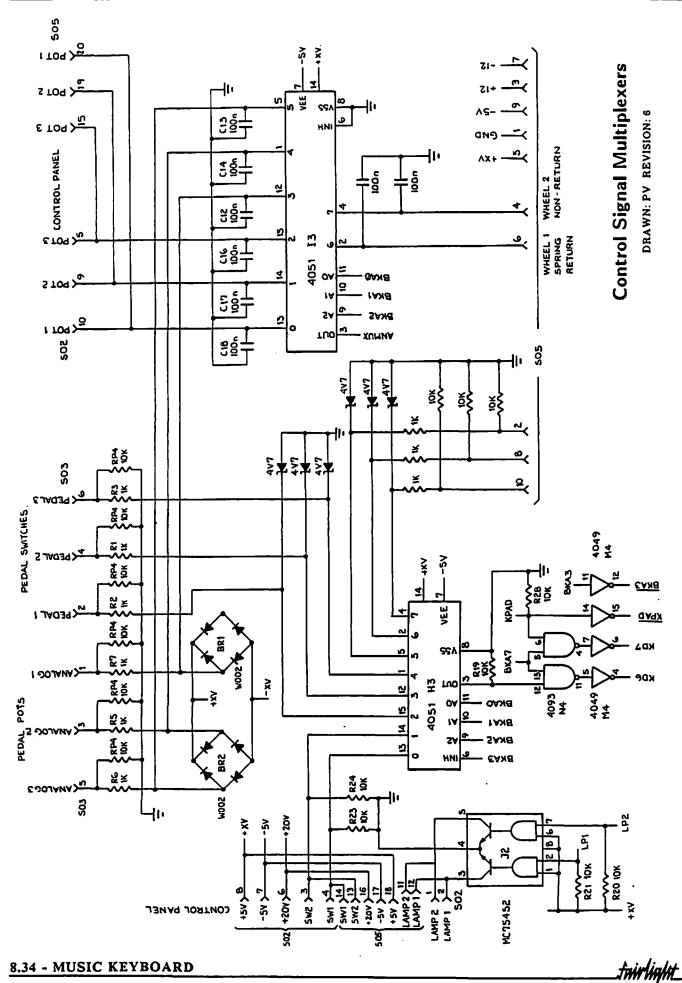

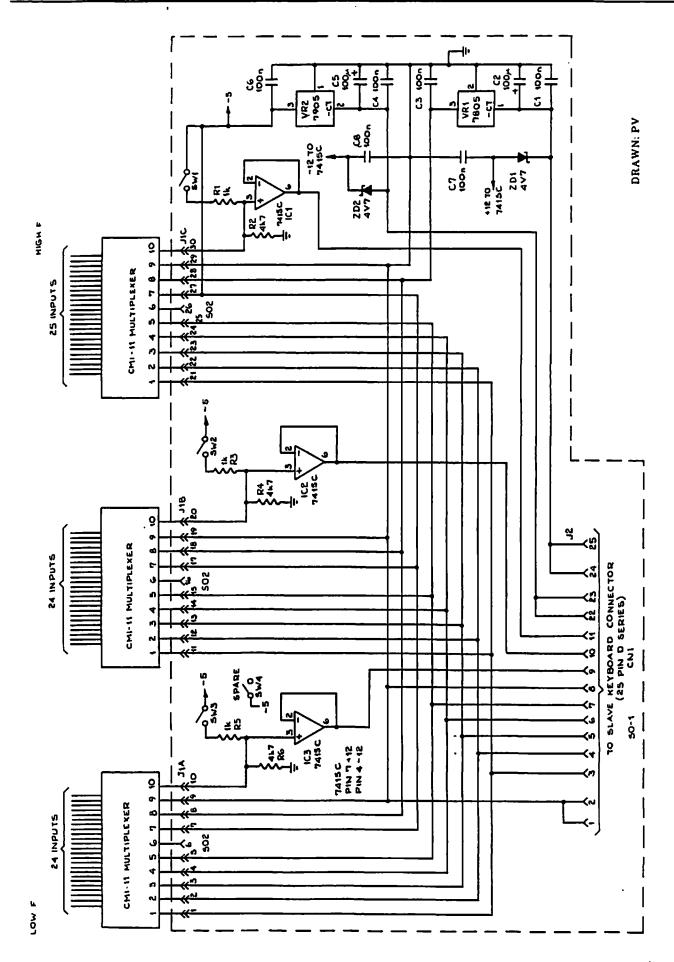

A multiplexed analog-to-digital converter samples the level of the three faders and two control wheels on the left-hand end of the keyboard as well as the three pedal inputs on the rear. Whenever one of these changes its level by more than a certain amount, a packet of MIDI control data is transmitted to the Mainframe giving the device number and the new level.

The two switches on the left of the keyboard and the three switches which plug into the rear of the keyboard are also scanned, and when any of these are opened or closed, suitable MIDI data is sent to the Mainframe.

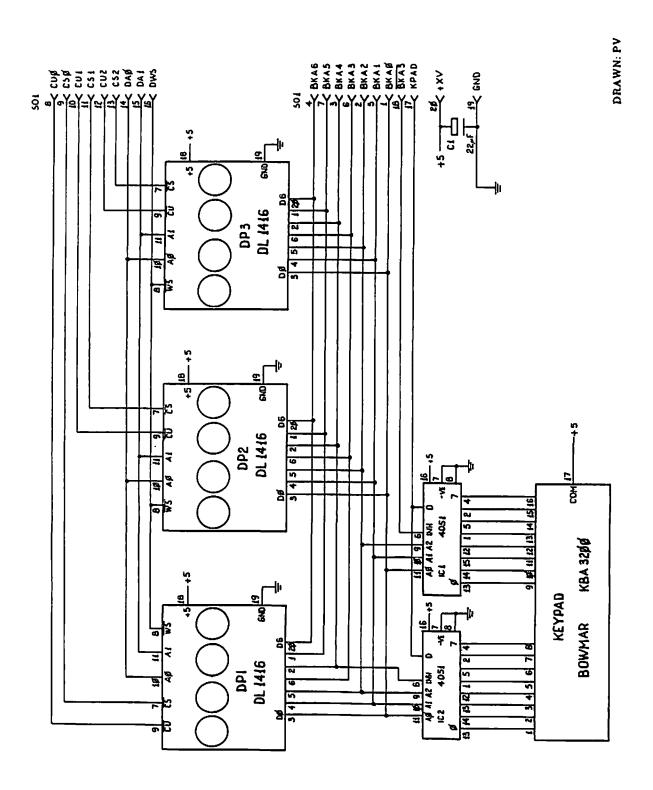

Pressing a key on the numeric keypad on the right-hand end of the keyboard sends a character to the Mainframe in exactly the same way as an alphanumeric key depression.

The alphanumeric LED display on the music keyboard is driven by the serial link coming from the Mainframe. The processor in the keyboard controls the displaying of individual characters as well as <rubout> and <clear>. When messages longer than the 12 digits of the display are required, a horizontal scrolling routine in the CMI system software is used.

#### Playing Programmed Music Sequences

When programmed sequences are played, P1 and P2 are involved. Data is read from disk and converted into MIDI frames and timing information. The MIDI data is fed into the MIDI input queue of the CMI - 28, and output under the control of the timing information.

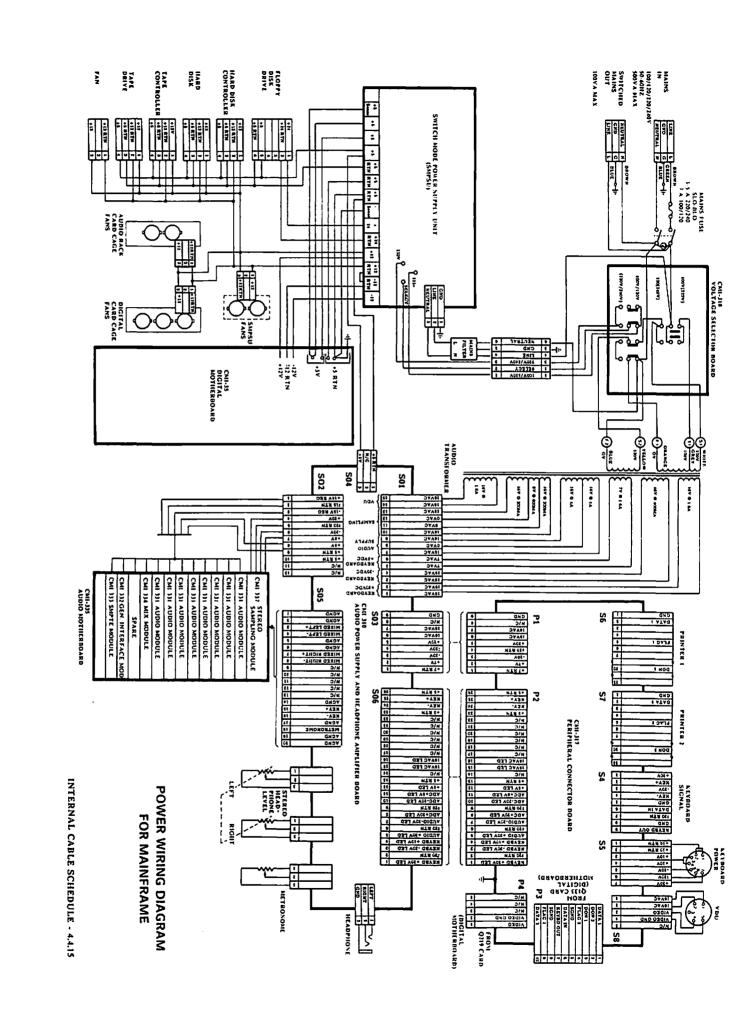

#### **ELECTRICAL**

Power Requirements

Mains Voltage: 100-120 or 200-250 switch selectable Mains Current: 2 amps @ 240V, 4 amps @ 120v

Mains Frequency: 50/60 Hz

#### AUDIO

Channel Outputs

Connector type: Cannon XLR 3 pin (balanced) Number of channels: 16 (maximum per mainframe)

Output level: +4dBm Output impedance: 600 ohms

Output load: Greater than 600 ohms

Mixed Line Output

Connector type: Cannon XLR 3 pin (balanced)

Output level: +4dBm with one channel playing

Switchable to -20dB attenuation.

Output impedance: 600 ohms

Output load: Greater than 600 ohms

Headphone Output

Connector type: 1/4" Stereo Phones

Amplifier: Stereo 500mW Signal: from mixer output.

Click Input

Connector type: Cannon XLR 3 pin

Level: I volt (min) to 20 volt (max) p-p

Frequency range: 200 Hz to 8KHz

Impedance: 10k ohms

Click Output

Connector type: Cannon XLR 3 pin Output signal: 5 volt square clock

SMPTE Input

Connector type: Cannon XLR 3 pin

Level: -20 to +10dBm Speed: 24 fps to 30 fps Impedance: 10k ohms

SMPTE Output

Connector type: Cannon XLR 3 pin

Output signal: +15dBm Impedance: 33 ohms

MIDI Inputs

MIDI standard opto-coupler receivers. MIDI standard 5-pin DIN sockets

#### **MIDI** Outputs

MIDI standard open collector current loop drivers MIDI standard 5-pin DIN sockets

#### Multi-Sync Outputs

Four sync outputs, pins 1,3,4 and 5 of the DIN socket TTL open collector signals

Clock or Drum-machine Controller Output

TTL open collector signals

Compatible with drum machines such as Roland

Pin 1; Run/Halt Pin 2; Earth Pin 3; Clock

Pin 4; Reset/Start Pin 5; n/c

#### Sampling Inputs

Connector type: Cannon XLR 3 pin

Input signal: Balanced

Sensitivity: -18 dBm required for full scale conversion

#### DIGITAL

Processors: Dual 6809 CPU

68000 Waveform Processor

68000 General Interface Processor

8 6809 Channel processors

Memory: 512K bytes CPU system RAM

16K Video RAM

512K bytes Waveform Processor Private RAM 64K bytes program RAM on each channel card 16K bytes General Interface Private RAM

2-14M bytes Waveform RAM

Floppy Disk: Mitsubishi M2896-63

8 inch double sided, single/double density Soft sectored, 128/256 bytes per sector

Hard Disk: 70M or 140M byte (unformatted) expandable as required SCSI bus compatible

Graphics Display: Bit mapped VRAM 512 x 256 pixels

Composite video output 1 volt p-p nominal 75 ohms impedance

Input/Output: Serial RS232C, 9600 Baud plus MIDI

#### **MECHANICAL**

Dimensions: Width 750 mm

Depth 480 mm Height 345 mm

Weight: 45 kilograms, depending on optioning

#### Introduction

Presented here is a list of cable connections and their allocated pins so that users may wire up their own cables, external cable connections only are shown, internal cables are presented elsewhere in this manual.

#### Cable schedule, Power Connections

The CMI is equipped with a standard IEC type three pin mains input power connector. Two pins are for active and neutral 100 to 240 volts AC only with the third being the earth or ground connection.

For feeding external devices a socket version of the IEC type connector is connected to the load side of the CMI mains switch. This provides up to 150VA of switched mains power.

#### **SCSI** Connector

The CMI comes equiped with an industry standard 50 way connector for devices on the SCSI bus.

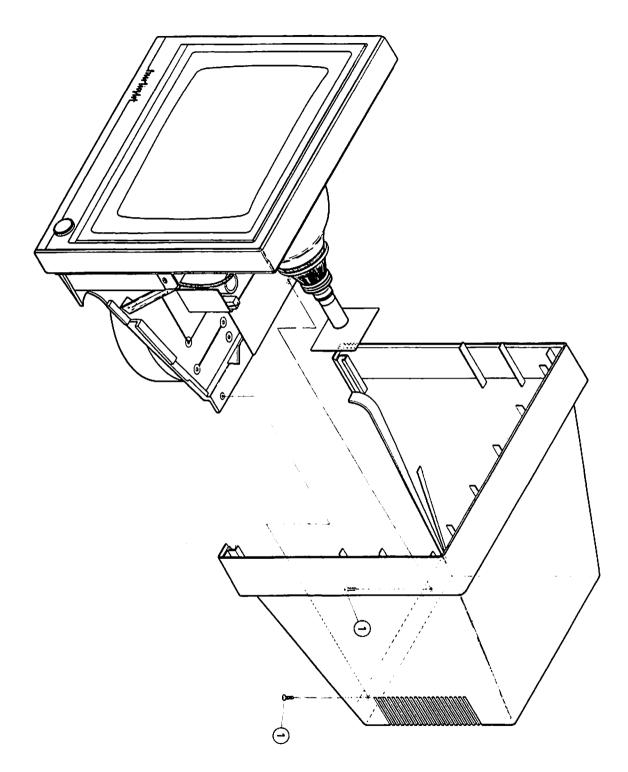

#### VDU Socket

The VDU socket is a 5 pin 'Belling Lee' type L1904A socket. This feeds the VDU with power and video signals.

| Pin no. | Function                 |

|---------|--------------------------|

| 1       | 16 volts AC power supply |

| 2       | 16 volts AC power supply |

| 3       | no connection            |

| 4       | video signal to monitor  |

| 5       | video ground             |

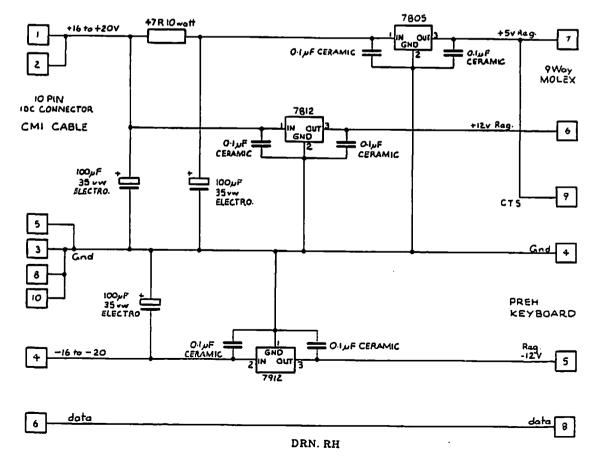

#### Keyboard Power

The music kayboard receives its power supply from the CMI mainframe via this connector. A 'CANNON' type 7 pin socket is used with the pins allocated as follows:

| Pin No. | Function               |

|---------|------------------------|

| 1       | 10 volts supply return |

| 2       | 10 volts supply return |

| 3       | +10 volts DC supply    |

| 4       | +10 volts DC supply    |

| 5       | -20 volts DC supply    |

| 6       | 20 volts supply return |

| 7       | +20 volts supply       |

#### Printer 1 and Printer 2

These sockets are for external connection of printers to the CMI. They are industry standard 'DB25S' type connectors.

| Pin no. | Function                     |

|---------|------------------------------|

| 1       | Protective or chassis ground |

| 2       | Data out                     |

| 5       | Clear To Send                |

| 7       | signal ground                |

| 20      | Data Terminal Ready          |

#### Keyboard Connector

The CMI music and alpha-numeric keyboards connect up via an industry standard 'DB9S' type connector.

| Pin No. | Function                            |

|---------|-------------------------------------|

| 1       | +20 volts supply for alpha KBD only |

| 2       | MIDI from music keyboard +          |

| 3       | -20 volts supply for alpha KBD only |

| 4       | MIDI from music keyboard -          |

| 5       | Ground                              |

| 6       | RS-232C data to CMI                 |

| 7       | Ground                              |

| 8       | Protective ground                   |

| 9       | Keyboard data from CMI              |

#### MIDI Inputs

The MIDI inputs are a standard 5 pin 180 degree DIN type socket.

| Pin No. | Function      |

|---------|---------------|

| 1       | no connection |

| 2       | no connection |

| 3       | no connection |

| 4       | MIDI in +     |

| 5       | MIDI in -     |

#### **MIDI Outputs**

The MIDI outputs are a standard 5 pin 180 degree DIN type socket.

| Pin No. | Function      |

|---------|---------------|

| 1       | no connection |

| 2       | ground        |

| 3       | no connection |

| 4       | MIDI out +    |

| 5       | MIDI out -    |

#### SYNC OUT

The SYNC OUT socket provides 4 sync outputs.

| Pin No. | Function   |

|---------|------------|

| 1       | sync out I |

| 2       | ground     |

| 3       | clock out  |

| 4       | sync out 2 |

| 5       | sync out 3 |

#### CLOCK out

The CLOCK output socket is a 5 pin 180 degree DIN type connector.

| Pin No. | Function      |

|---------|---------------|

| ı       | Run/Stop      |

| 2       | ground        |

| 3       | clock         |

| 4       | Reset/start   |

| 5       | no connection |

#### SMPTE IN

This socket is an 'XLR type three pin socket.

| Pin No. | Function   |

|---------|------------|

| 1       | ground     |

| 2       | SMPTE in - |

| 3       | SMPTE in + |

#### SMPTE out

This connector is a panel mount 'XLR' type three pin plug.

| Pin No. | Function    |

|---------|-------------|

| 1       | ground      |

| 2       | SMPTE out - |

| 3       | SMPTE out + |

#### **METRONOME**

This is a panel mount three pin 'XLR' type plug.

| Pin No. | Function      |

|---------|---------------|

| 1       | ground        |

| 2       | ground        |

| 3       | metronome out |

#### CLICK in

A three pin 'XLR' type socket is used for Click Track input.

| Pin No. | Function       |  |

|---------|----------------|--|

| 1       | ground         |  |

| 2       | no connection  |  |

| 3       | Click Track in |  |

#### CLICK out

An 'XLR' type three pin panel mount plug is used to connect Click Track out to external devices.

| Pin No. | Function        |  |

|---------|-----------------|--|

| 1       | ground          |  |

| 2       | ground          |  |

| 3       | Click Track out |  |

## **EXTERNAL CABLING**

#### MIXER And AUDIO Outputs

The Audio and Mixer outputs are connected via 'XLR' type three pin panel mounted plugs.

| Pin No. | Function |  |

|---------|----------|--|

| 1       | ground   |  |

| 2       | Output - |  |

| 3       | Output + |  |

#### SAMPLER Input

The Sampler connects via three pin 'XLR' type sockets.

| Pin No. | Function          |  |

|---------|-------------------|--|

| 1       | ground (floating) |  |

| 2       | Audio Input -     |  |

| 3       | Audio Input +     |  |

### **Contents**

| Q209 Central Processor                  | 2.2     |

|-----------------------------------------|---------|

| Q133 Control Card                       | 2.3     |

| Q256 256K RAM Card                      | 2.4     |

| QFC9 Floppy Disc Controller             | 2.5     |

| Q219 Lightpen Graphics Card             | 2.6     |

| Q137 Front Panel                        | 2.7     |

| Q777 SCSI Interface                     | 2.8     |

| CMI-28 General Interface                | 2.9     |

| CMI-32 Channel Support Card             | 2.10    |

| CMI-31 Channel Card                     | 2.11    |

| CMI-33 Waveform Processor               | 2.12    |

| CMI-39 Waveform RAM 256K/1M Word        | 2.13    |

| CMI-35 Digital Mother board             | 2.14    |

| Mainframe assembly rear and bottom view | 2.14.19 |

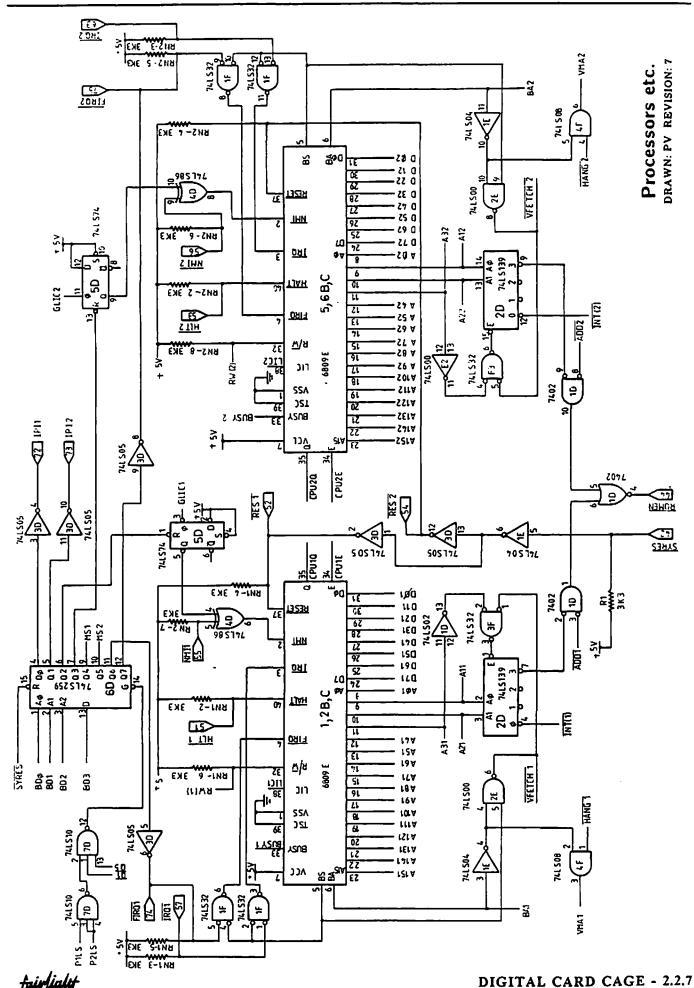

## COCOCO Dual 6809 Central Processor

| IIII V44C (10II                   | 2.2,7 |

|-----------------------------------|-------|

| Master timing signals             | 2.2.2 |

| Dynamic memory timing signals     | 2.2.2 |

| Data and address bus multiplexing | 2.2.2 |

| Interrupt and strobe generation   | 2,2.3 |

| Direct memory access              | 2.2.3 |

| Vector-fetch decoders             | 2.2.3 |

| Processor system control          | 2.2.3 |

| Automatic map switching           | 2.2.4 |

| Hardware trace                    | 2.2.4 |

| Indivisible instructions          | 2.2.4 |

| Link options                      | 2.2.5 |

| Schematic Diagrams                | 2.2.6 |

#### Introduction

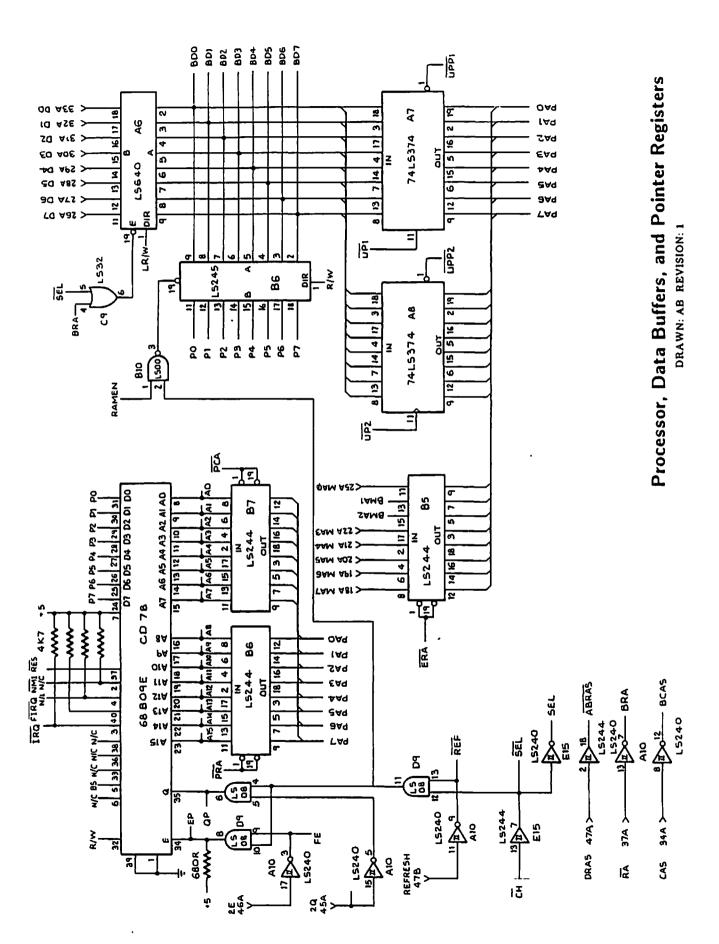

The Q209 contains the dual 6809 processors, on board processor communication hardware entailing indivisible instructions, processor readable identification / map state, interprocessor interrupts, automatic map switching FUSE register and hardware trace logic to enable single stepping for software debugging.

The Dual Processor card multiplexes each processor onto a common address and data buss in an interleaved manner, each processor therefore may simultaneously access the same memory location without any contention, if the memory is mapped onto both processors. (See Q256 functional description)

The memory addresses are issued to the buss 225 nanoseconds prior to the access cycle, allowing addresses to be mapped by the memory card, to allow for accessing greater than 64K of RAM.

Many global timing signals are issued from the processor for general buss control.

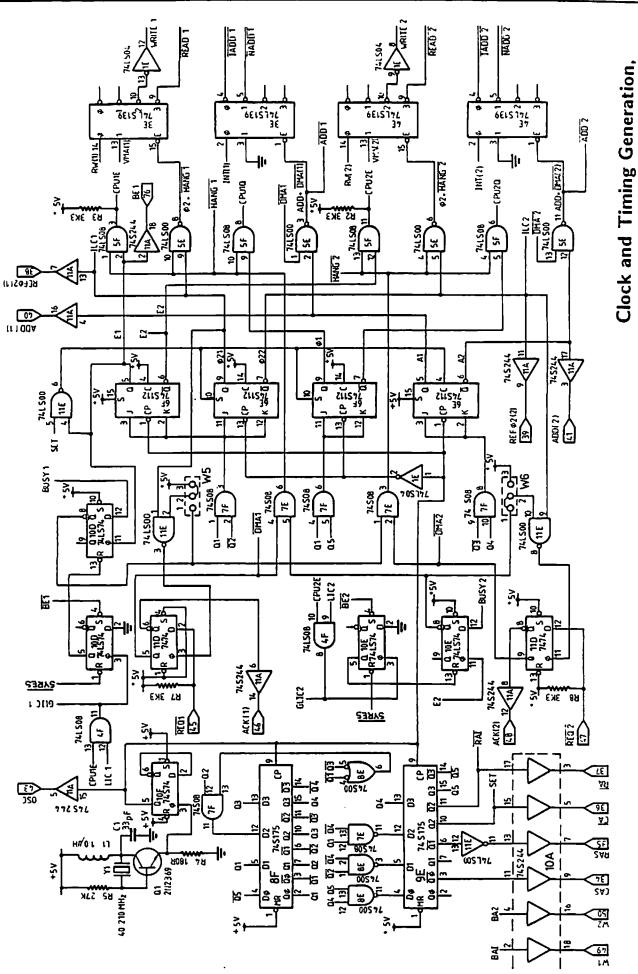

### Master Timing Signals

(refer schematic Q209-00)

All system timing signals are derived from crystal-controlled 40MHz oscillator Q1. Flip-flop 10F derives two opposite phase 20 MHz square waves. Quad D-type latch D2, together with the NAND gate in 7F, forms a 10 state Johnson, or twisted-tail ring counter. Each state is of 50ns duration. The system signals are decoded by NAND gates in 8E from the output of this counter.

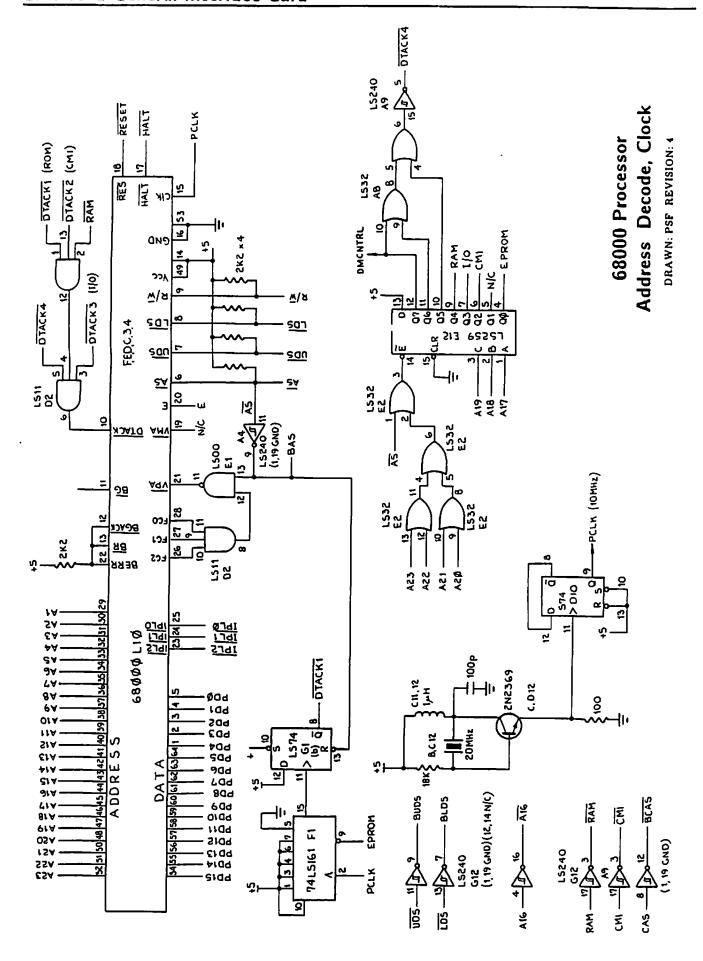

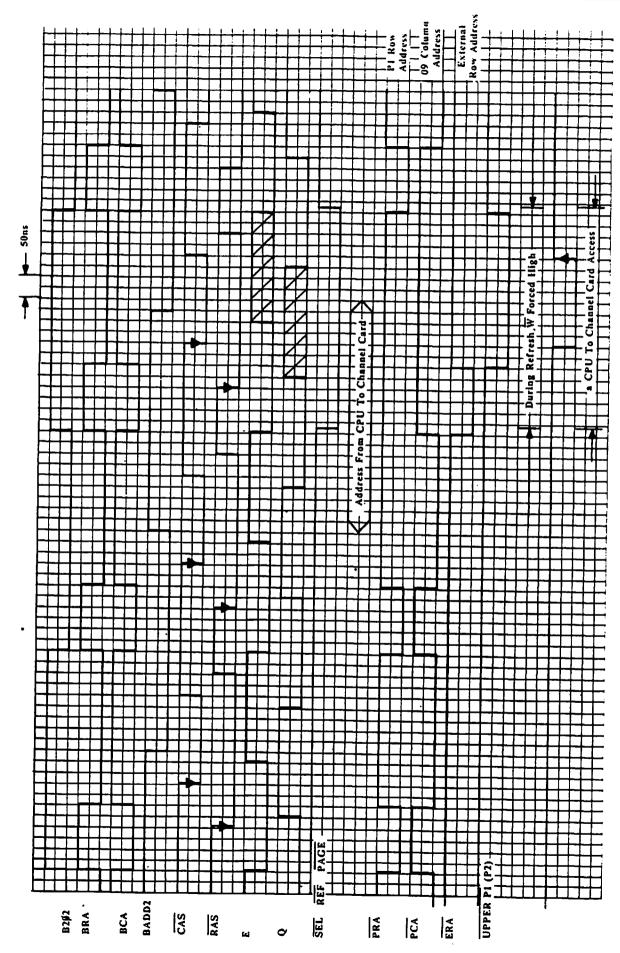

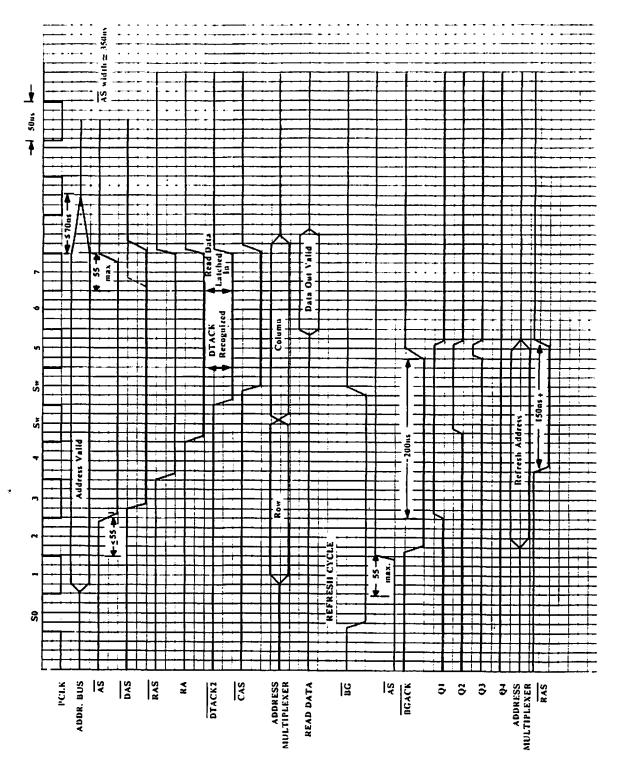

## Dynamic Memory Timing Signals

(refer schematic Q209-00)

Four non-inverting buffers of 10A are driven by latch E1 to provide CAS(Column Address Strobe), RAS (Row Address Strobe), CA (Column Address, active low) and RA (Row Address, active low). RAS is delayed relative to CAS by about 20ns by the propagation delay of 11E. RA and CA are complementary.

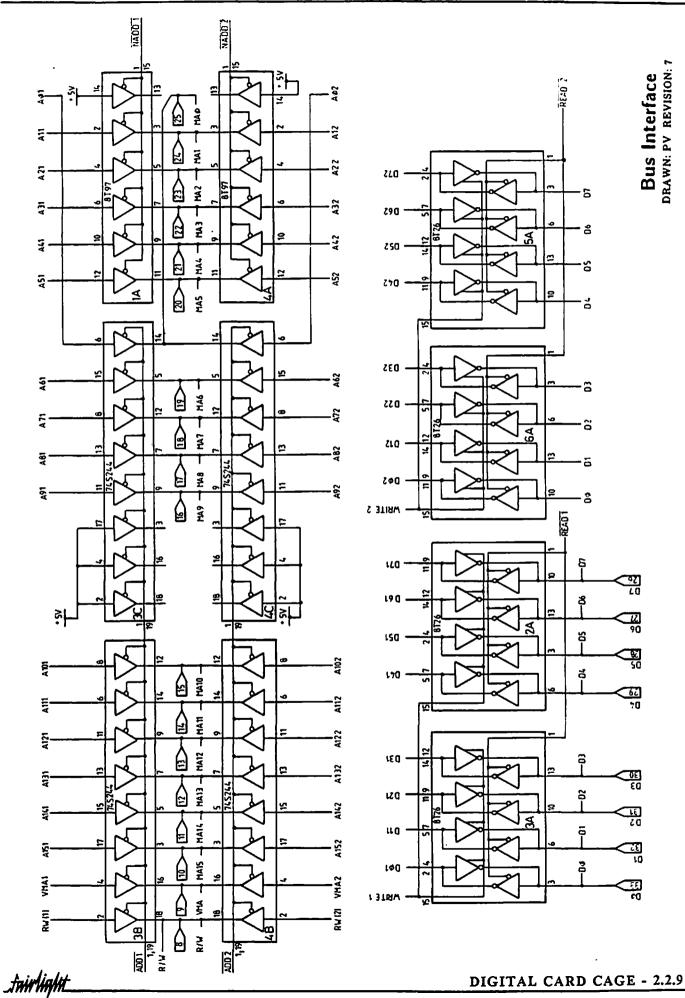

### Data and Address Buss Multiplexing

(refer schematic Q209-03)

Flip-flop 6F, along with associated gating, generates the 6809's E signals. The system address buss is multiplexed by the ADDRESS signals ADD1 and ADD2, (active low). One-of-four decoders 3E and 4E are used to enable the appropriate address and data buffers, to perform the multiplexing. The data buffer enable signals WRITE1, WRITE2, READ1, READ2 are generated by logical combinations of R/W, VMA, processor phase 2 and DMA lines. The address buss is actually multiplexed 4 ways, as the vectored interupt system may also acquire the buss' least significant bits of the address buss for either processor's vector fetch cycle. The address buffer enables are a function of the Address signal and the Interupt acknowledge.

Phase 2 reference and Address references for each Processor are feed to the buss via buss drivers.

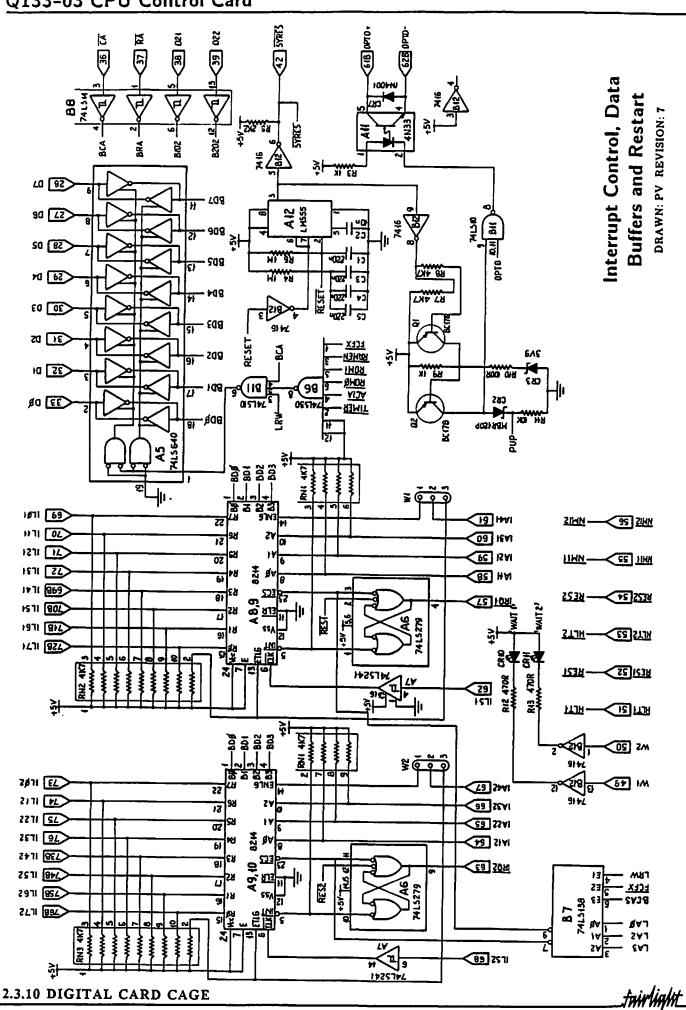

## Interrupt Strobe Generation (refer schematic Q209-02)

Dual D-type flip-flop 9D and 3-input AND gate 8D feed Interrupt Strobe pulses to the buss. These are used by the Priority Interrupt Control Units (PICUs) used to provide vectored interrupts, and also to strobe the vector address latches 8A and 9A. The PICUs are located on the Q133 card. These signals strobe the priority latches continuously, until an interrupt is acknowledged. In this way the Interrupt Priority is maintained at its latest level regardless of delay between an interrupt request being received by the PICU and the associated vector-fetch cycle being executed.

#### **Direct Memory Access**

(refer to drawing Q209-00)

DMA requests for each processor are clocked into flip-flop 11D on the falling edge of the phase 2 signal of the respective processor. DMA acknowledge is sent to the buss via buffers and drive signals to the processors are suspended in the phase 1 state for the duration of the DMA cycle. The maximum permissible DMA duration is 5 microseconds. Worst-case DMA latency is 1 microsecond. Latency is the time required to service the request.

#### Vector-Fetch Decoders

(refer to drawing Q209-01)

The vector state of the processors are decoded by the one-of-four decoders, 2D and NOR gates in 1D. These correspond to addresses in the range FFF0 to FFFF. They correspond to the processor fetching vectors FIRQ, NMI, SWI1, SWI2, SWI3, IRQ and RESTART. The Restart vectors come from ROM so when this is sensed the ROM is enabled and the ram disabled. This is achieved by the ROMEN signal on buss pin 44. On detection of an Interrupt Request vector address from the processor, decoder 2D causes the normal address buss drivers for bits 1 to 4 to be disabled and the Interrupt Address buffers to be enabled in lieu.

#### **Processor System Control**

These general functions are controlled through ports at the following locations ...

\$FC5E Indivisible instructions read \$FC5E Various CPU functions write \$FC5F Map status and CPU ID read \$FC5F Automatic map switching FUSE write

The ID can be read to determine the status of the memory map switching hardware. The CPU ID bit can be read by the CPU to find out which CPU is running the program.

The bits are defined as

- D0 CPU ID 0=P1 1=P2

- D1 P1 map status 0=map B, i=map A

- D2 P2 map status

- D3 zero

- D4 n/c (indeterminate)

- D5 n/c

- D6 n/c

- D7 n/c

The "Various CPU functions" is an 8 bit register in which each bit may be independently written to. This register is at location 6D, and it is decoded by devices at 9B and 7A. When written to, the bit address is selected by the 3 least significant bits of the data byte. The state of data bit 3 determines whether the bit is set or cleared.

The four functions provided per processor from this register are:-

- 0+P interprocessor interrupt

- 2+P hardware trace

- 4+P map switch select

- 6+P fast interrupt request

where P is "0" for processor 1 and "1" for processor 2

Fast interrupts may be generated either by an external signal or from the bus. The on-card FIRQ must be reset by the processor concerned, by writing a reset bit to the register.

#### Automatic Map Switching

(refer schematic Q209-02)

The memory cards support hardware selectable memory maps. The processors can control the  $A/\overline{B}$  select lines, allowing automatic switching between "user(B)" and "system(A)" maps.

Whenever an interrupt or processor restart occurs, the A map will be automatically selected. During an interrupt, the switching will occur after the registers are stacked and before the interrupt vector is fetched.

A FUSE location is provided which causes the map to be switched after a specified number of CPU clock cycles have elapsed. These counters are at 8C for CPU1 and 9C for CPU2. The data written to these counters is buffered by the buffer at 7C. The map changed to is determined by the value of the map switch select bit. The map switch will occur after the Nth CPU cycle after the FUSE register write. The delay is required so that a known number of instructions can be executed for house keeping before the CPU's memory is swapped.

Hardware also selects the A map whenever DMA occurs.

#### Hardware Trace

An NMI may be generated after each instruction execution for software debugging. This is done by flip-flops 5D and half of AND gate 4F. This function is enabled under software, by access to \$FC5E.

Enabling this function inverts the NMI signal from the front panel, so that if the trace hardware is left in the triggered state, front panel NMI requests will still be recognized, but on the opposite edge ( since NMI is an edge triggered input ).

#### Indivisible Instructions

(refer to schematic Q209-00)

For the test-and-set and double byte load/store instructions to be effective, the processor not executing the instruction must not be able to alter the flag memory location in question. To this end, the execution of these read/modify/write instructions effectively hangs the other processor for its duration, thus preventing race conditions.

This is achieved by flip-flops 10D, 10E, associated gating and the BUSY outputs from the processors. The BUSY outputs are active when the test and set instruction is executed, and the other processors clock is stopped for its cycle, in the same manner as for DMA transfers. The flip-flops associated with this are reset at power on to enable the clocks to the 6809's to allow them to be internally reset, at power on reset. To enable this function the instruction to be made indivisible must be immediately preceded by a read from hardware location \$FC5E. No interrupt must be allowed to occur between the read and the instruction. This function is automatically disabled at the end of the instruction following the read.

#### Link Options

The links have the following functions:

| Option | CPU | LINK  | Function                                    |

|--------|-----|-------|---------------------------------------------|

| WI     | P1  | 1-2 * | enable map select output                    |

|        |     | 2-3   | disable                                     |

| W2     | P1  | 1-2 * | enable DMA to select A map                  |

|        |     | 2-3   | disable                                     |

| W3     | P2  | 1-2 * | enable map select output                    |

|        |     | 2-3   | disable                                     |

| W4     | P2  | 1-2 * | enable DMA to select A map                  |

|        |     | 2-3   | disable                                     |

| W5     | Pl  | 1-2   | disable P1 DMA during indivisible P2 cycles |

|        |     | 2-3 * | enable                                      |

| W6     | P2  | 1-2 * | disable P2 DMA during indivisible P1 cycles |

|        |     | 2-3   | enable                                      |

These links are set by PCB traces in the positions marked by \* . Links

\_twirlight\_

\_tairlight\_

DRAWN: PV REVISION: 7

DMA Control

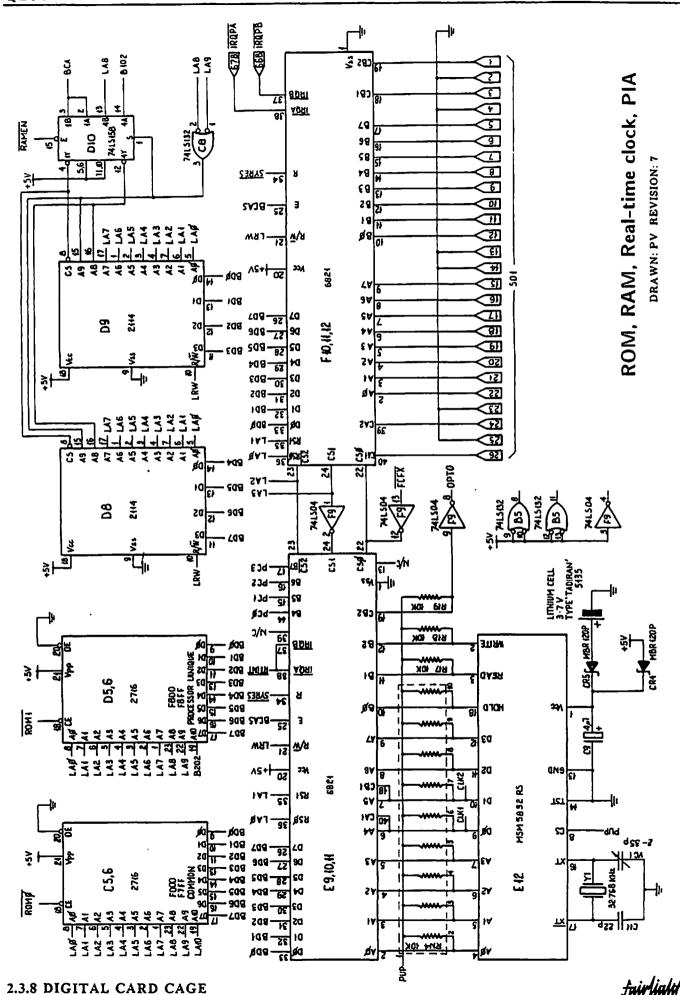

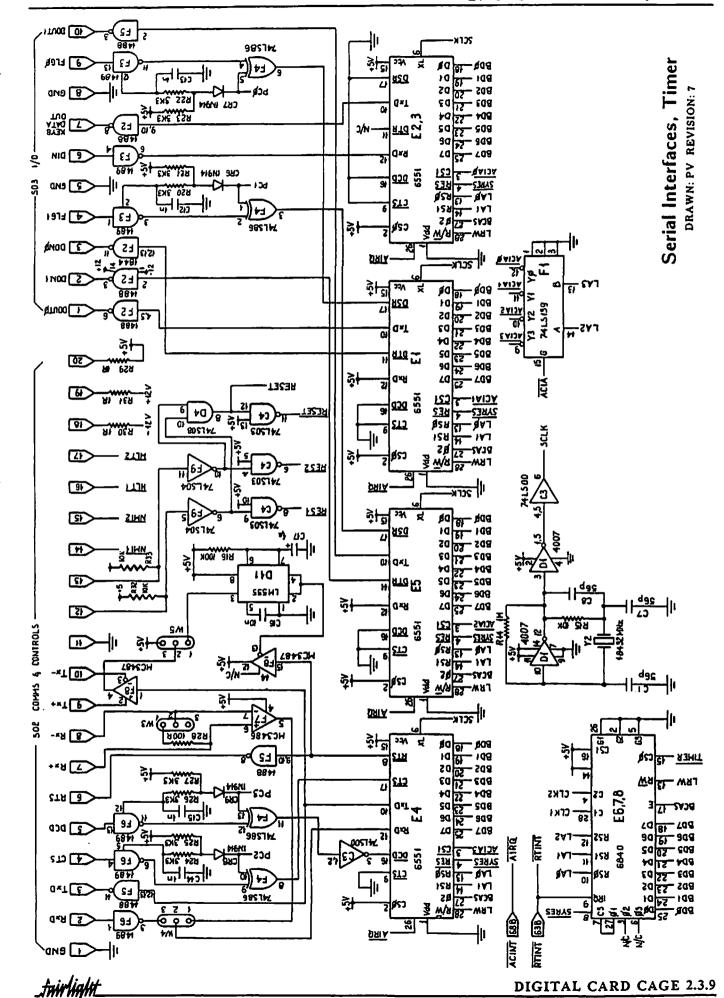

# Q133 CPU Control Card

| Introduction                  | 2.3.2 |

|-------------------------------|-------|

| Address map                   | 2.3.2 |

| Restart and interrupt vectors | 2.3.2 |

| Debug monitor ROM             | 2.3.2 |

| System boot/disk ROM          | 2.3.4 |

| Address decoding              | 2.3.4 |

| RAM refresh control           | 2.3.4 |

| Static RAM                    | 2.3.5 |

| EPROM                         |       |

| ACIA                          | 2.3.5 |

| PIA                           | 2.3.5 |

| Manual controls               | 2.3.6 |

| Power-on reset                |       |

| Interrupt priority logic      |       |

| Schematic diagrams            |       |

#### Introduction

The CPU Control Card provides several support functions required by the CPU card. These include startup and bootstrap ROM, 4 serial communication ports, interrupt prioritisation, dynamic RAM refresh, day/date/time of day clock, Pl DMA daisy chain, and a parallel port.

#### Address Map

The Debug Card occupies the last 4K bytes of the 65K byte memory addressing space and is set up as follows:-

ADDRESS (HEX) **FUNCTION** F000-F7FF Rom0 common rom F800-FBFF Rom1 processor unique FC00-FCEF Available for peripherals FC80-FC8F ACIA registers FC90-FC97 Timer (6840) FCF0-FCFF PIA registers, user and clock **FCFC** CPU#1 interrupt prioritiser **FCFD** CPU#2 interrupt prioritiser FD00-FEFF Shared 512 byte RAM FF00-FFFF Unique 256 byte RAM for each processor

#### Restart and Interrupt Vectors

RAM space allocated uniquely to each processor provides independent restart and interrupt vectoring. The vector locations are as follows:

| ADDRESS (HEX)    | VECTOR                |

|------------------|-----------------------|

| FFFE/F           | Restart               |

| FFFC/D           | NMI                   |

| FFFA/B           | SWII                  |

| FFF8/9           | Unused                |

| FFF6/7           | FIRQ                  |

| FFF4/5           | SWI2                  |

| FFF2/3           | SWI3                  |

| FFF0/I           | Unused                |

| FFEE/F (lowest)  | IRQ level 7           |

| FFEC/D           | IRQ level 6           |

| FFEA/B           | IRQ level 5           |

| FFE8/9           | IRQ level 4           |

| FFE6/7           | IRQ level 3           |

| FFE4/5           | IRQ level 2           |

| FFE2/3           | IRQ level 1           |

| FFE0/I (highest) | IRQ level 0 (highest) |

#### **Debug Monitor**

The Q133 contains two 2K ROMs that contain all the basic driver and initialization routines, such as loading the Disc drivers and Q256's maprams.

The monitor ROM occupies 1K bytes from F000 to F3FF and may be accessed by either processor. Processor-unique workspace RAM is used by the monitor so both processors can be executing the monitor independently.

| Commands                 | •                                                    |

|--------------------------|------------------------------------------------------|

| /                        | Reopen last open address as a 1-byte unit            |

| AAAA                     | Open 2-byte unit at address AAAA                     |

|                          | Reopen last open address as a 2-byte unit            |

| \$A                      | Open CPU accumulator A                               |

| \$B                      | Open CPU accumulator B                               |

| \$X                      | Open CPU index register X                            |

| \$P                      | Open CPU program counter                             |

| \$H                      | Open user SWI handler address                        |

| \$C                      | Open CPU Condition Code register                     |

| \$D                      | Open CPU D register (A,B concatenated)               |

| \$Y                      | Open CPU index register Y                            |

| \$U                      | Open CPU User Stack pointer U                        |

| \$S                      | Open CPU Stack pointer S                             |

| \$R                      | Open program segment Relocation Register             |

| \$G                      | Open CPU direct page register                        |

| SF                       | Open monitor flag byte                               |

| <return></return>        | Close the open location                              |

| <li><li>ed&gt;</li></li> | Close current, open next location                    |

| <b>y</b>                 | Close current, open previous location                |

| >                        | Close current, take branch offset and open           |

| @                        | Open location pointed by current location            |

| AAAA;B                   | Insert a breakpoint at address AAAA                  |

| ;L                       | List all active breakpoints                          |

| AAAA;D                   | Delete breakpoint at address AAAA                    |

| ;C                       | Clear all breakpoints                                |

| AAAA;T                   | Insert tracepoint at location AAAA (non-stopping     |

|                          | breakpoint)                                          |

| AAAA;K                   | Kill tracepoint or breakpoint at AAAA                |

| AAAA;G                   | Start a user program at address AAAA                 |

| ;P                       | Proceed from breakpoint, abort, or call              |

| AAAA;O                   | Calculate branch offset from open location to        |

|                          | address AAAA                                         |

| HH;F                     | Fill memory from beginning address to end            |

| <b>-</b>                 | address                                              |

| BEG ADDR                 | User prompt for beginning address                    |

| END ADDR                 | User prompt for end address                          |

| <ctrl x=""></ctrl>       | Abort current command line, take no action           |

| <                        | Close current location, return to sequence start     |

| •                        | and open                                             |

| AAAA,R                   | Relocate address AAAA by register R. R may be any    |

|                          | of the CPU registers, the user relocation register,  |

|                          | the monitor flag byte or the currently open location |

| AAAA.                    | Relocate address AAAA by Relocation Register \$R     |

| :                        | Same as linefeed (CTRL J) except that no new line    |

| •                        | is taken,                                            |

|                          | and neither the address nor contents of the next     |

|                          | location is displayed                                |

| AAAA#LL                  | Memory dump of LL lines (16 bytes/line) starting     |

| <del>-</del>             | from, address AAAA                                   |

| ' <ascii chr=""></ascii> | Input ASCII character value instead of hex value     |

| '                        | for any of the above commands                        |

| The 6809 monitor w       | ill also accept input of signed hex numbers.         |

|                          | · · · ·                                              |

.twirlight\_

System Boot/Disk ROM

This ROM is used by CPU#2 for disk booting operations and occupies locations F800 to FBFF in the unique ROM space for CPU#2.

The following functions calls are provided:-

- \* Boot load QDOS operating system from disk

- \* Initialise disk controller

- \* Read full last sector

- \* Read partial last sector

- \* Read verify (CRC check only)

- \* Write and verify CRC

- \* Restore head (seek track 0)

- \* Seek to specified track

- \* Write test

- \* Write D.D. mark to sector

- Write sectors and verify CRC

- \* Write sectors and don't verify CRC

- \* Check and abort if non-recoverable error

This ROM contains the code to load the actual disk drivers into system RAM. The driver routines themselves are stored in RAM after being loaded from the ROM on the QFC9 floppy controller card, the Q077/Q087 Hard Disk card if present and the Q777 SCSI Controller card.

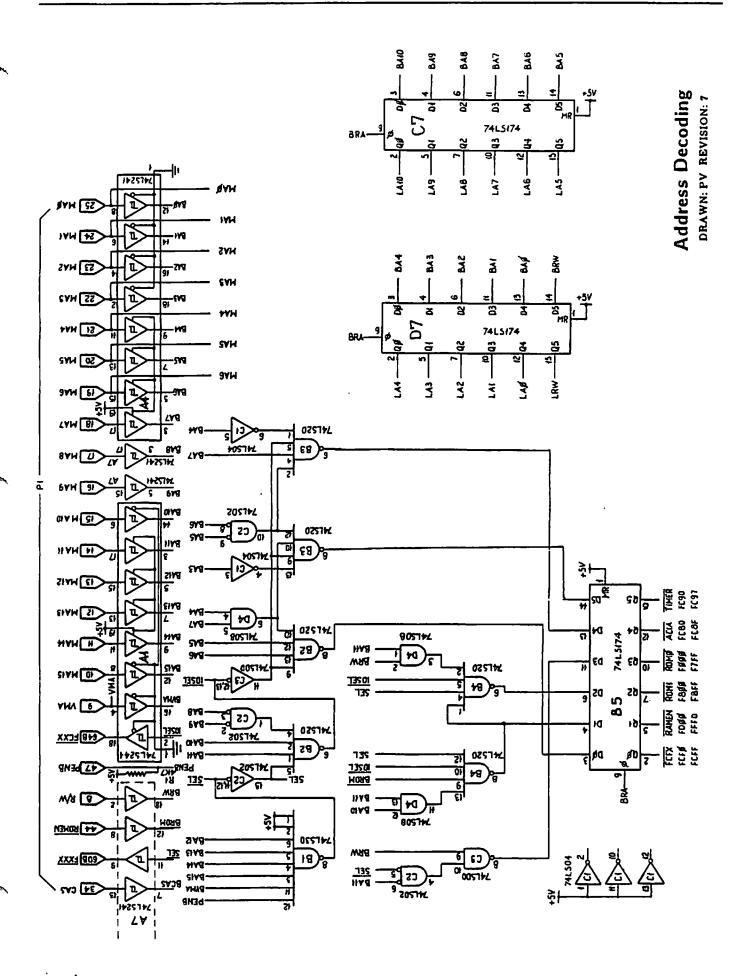

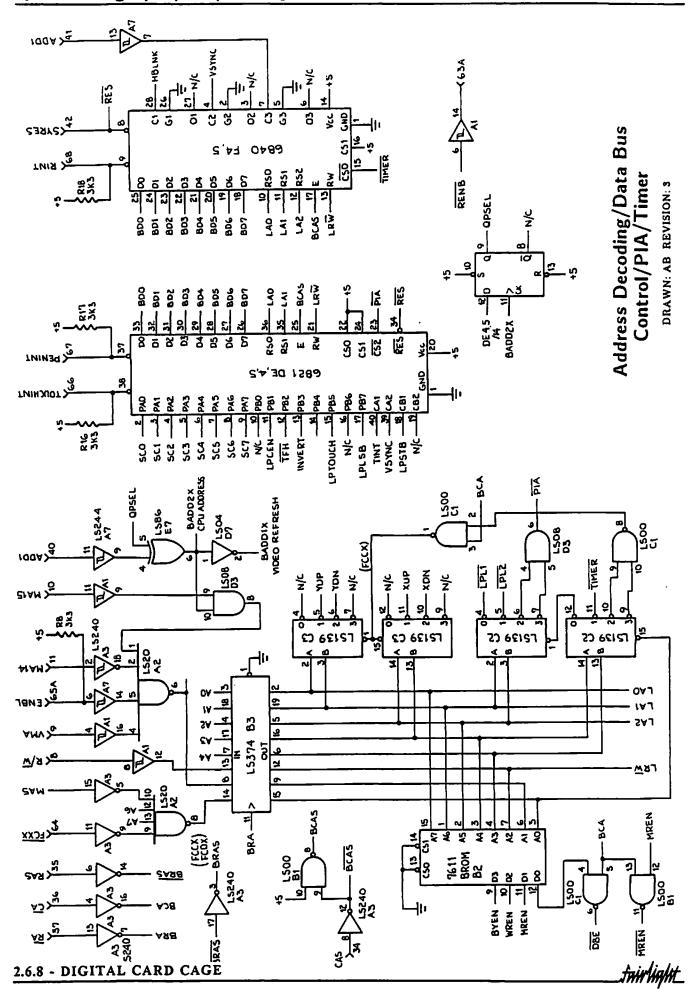

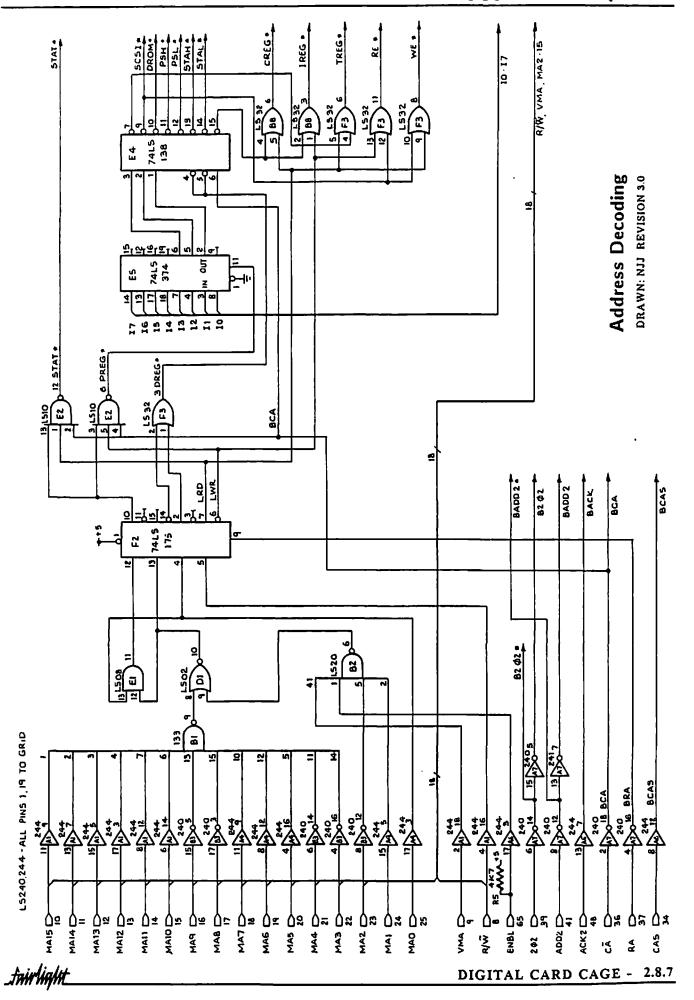

#### Address Decoding

(refer schematic Q133-00)

The System Address Buss is buffered by non-inverting buffers Al and A4. NAND gate Bl generates an output (asserted LOW) when an address in the range FXXX is detected. This is fed out to the buss on edge connector pin 60B. Further decoding by combinational logic at B4, D4, B3, C2 and C1 generate select signals for the two EPROMS, ROM0, ROM1.

Selection of the on-card static RAM and peripheral devices in the FCFX range are also decoded.

These six select signals are latched by hex flip-flop B6. Hex flip-flops C7 and D7 latch the 11 low-order address bits, as well as the READ/WRITE signal. When any of the on-board devices are read from, inverting data buss transceiver A5 drives the buss. (See drawing Q133-03). At other times, A5 buffers the data into the card.

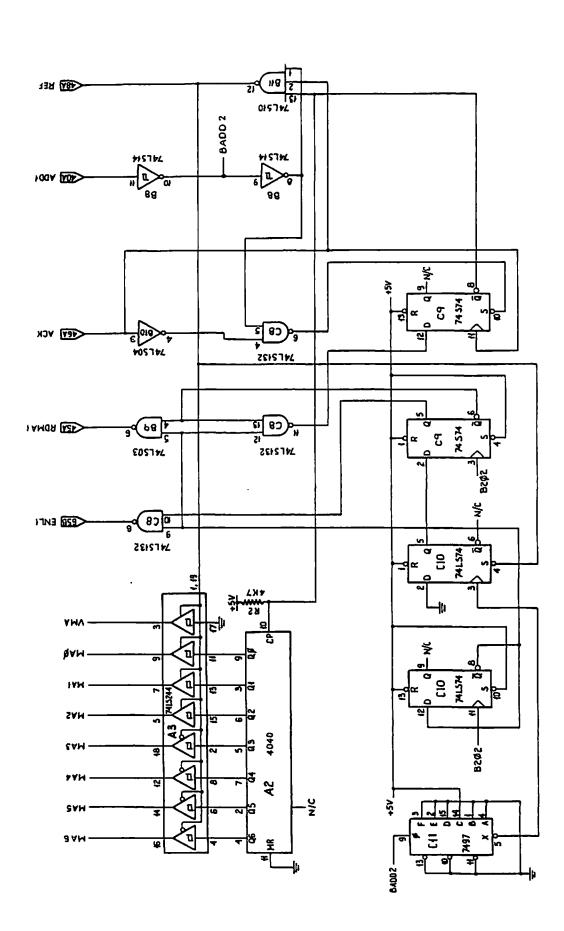

#### RAM Refresh Control

Rate multiplier C10 is configured to produce a 1 microsecond pulse every 16 microseconds. This output generates a DMA request for Processor 1 (RDMA), via DMA hardware at C8, B10 ,B5 and C4. The refresh has the highest priority in the P1 DMA daisy chain.

The ENL signal, (Enable Next Level), indicates to the next device along the daisy chain when it may make DMA requests. It normally goes low every second P1 cycle, but if a refresh request is pending, the low pulse is inhibited.

When this request is acknowledged by the ACK1 buss signal from the Q209 CPU (asserted HIGH) flip-flop B10 generates a /REF (Refresh, asserted LOW) signal on the buss, which signals a refresh cycle to the dynamic RAMs in the system. At the same time, the output of the refresh address counter A2 is driven onto the buss by tri-state buffers A3. At the completion of the refresh (DMA) cycle, the refresh address counter is incremented ready for the next cycle.

#### Static RAM

(refer schematic Q133-01)

A small amount of static RAM is provided for use as scratchpad during disk calls and monitor firmware execution. It is organised as follows:

CPU #1 FF00-FFFD CPU #2 FF00-FFFD Both FD00-FEFF

The addressing function for this purpose is generated by multiplexer C9 which is driven by an OR funtion of address bits 8 and 9. The RAM itself is in the form of two IK X 4 devices at D8 and D9.

#### **EPROM**

Four kilobytes of U.V. erasable ROM are used. These are 2716s/2516 single 5 volt supply type.

Their functions are:

| Location | Address Range | CPU # | Function      |

|----------|---------------|-------|---------------|

| D2       | F800-FBFF     | 1     | Startup       |

| D4       | F800-FBFF     | 2     | Disk boot     |

| D5       | F400-F7FF     | Both  | I/O functions |

| D6       | F000-F3FF     | Both  | Debug monitor |

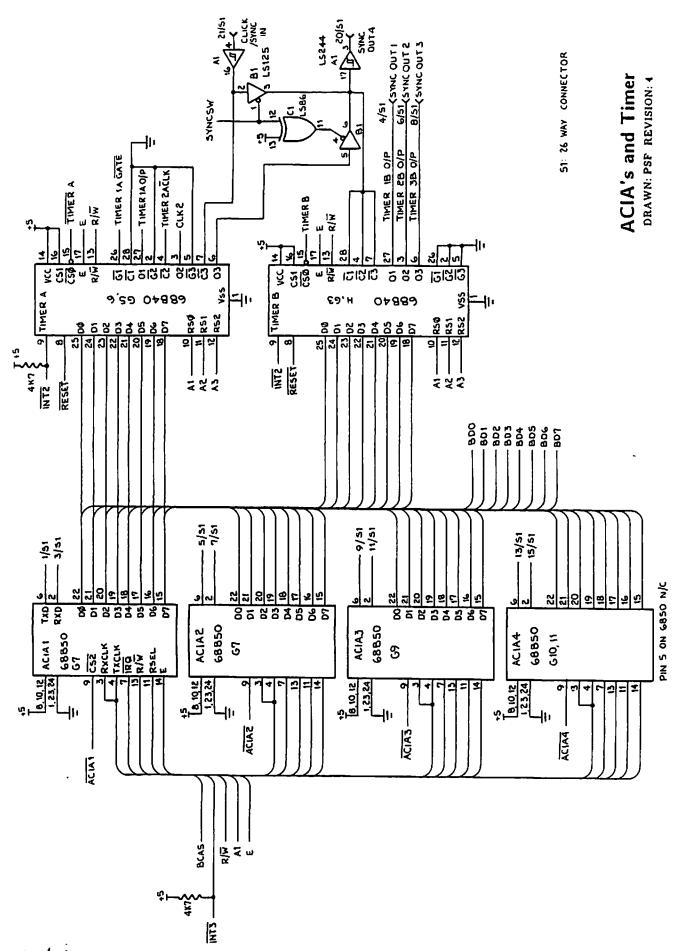

## ACIAS (Asynchronous Communications Interface Adapter) (refer schematic 0133-02)

6551 ACIAs at E4, E5, E1, E2, E3 are used to receive and transmit serial data. The BAUD rate is determined internally via internal dividers, from the baud-rate generator master 1.8432MHz oscilator at D1.

Interrupts generated by the ACIAs go to the system buss via pin 68B of the edge connector.

Data input and output level conversion for the RS232 standard is provided by circuitry on Sheet 3.

The 6551 used for keyboard data is at location E2, 3. The ACIAs at E4 and E5 have optional RS422 tranceivers at F7 and F8 as well as RS232, at F6 and F5. The 555 timer at D10 is used in the RS422 buss timeout control.

#### PIA (Peripheral Interface Adapters)

(refer schematic Q133-01)

PIA (F10,11,12) is used to provide two general purpose parallel ports. Peripheral connections are made through a 26-way ribbon cable connector on the front of the card.

Interrupts from the PIA are presented to the buss via pins 66B and 67B.

PIA (E9,10,11) is used to interface the clock/calender chip at E12. This clock has a 3.7 volt Lithium cell to maintain the time when the computer is turned off. The battery is not rechargeable and must be replaced when flat. Battery life is approximately 3 years.

Diodes CR5 and CR4 isolate the battery from the 5 volt supply, so that the battery is only connected to the clock when the 5 volt supply drops. Transistors Q2, Q1 on drawing Q133-03, and associated components interface the PIA's signal levels to the clock and control the power-down function of the clock so that no false writes occur at power-on and off. An optically isolated power down signal is available at connector pins 61B and 62B, from the opto-isolator at A11.

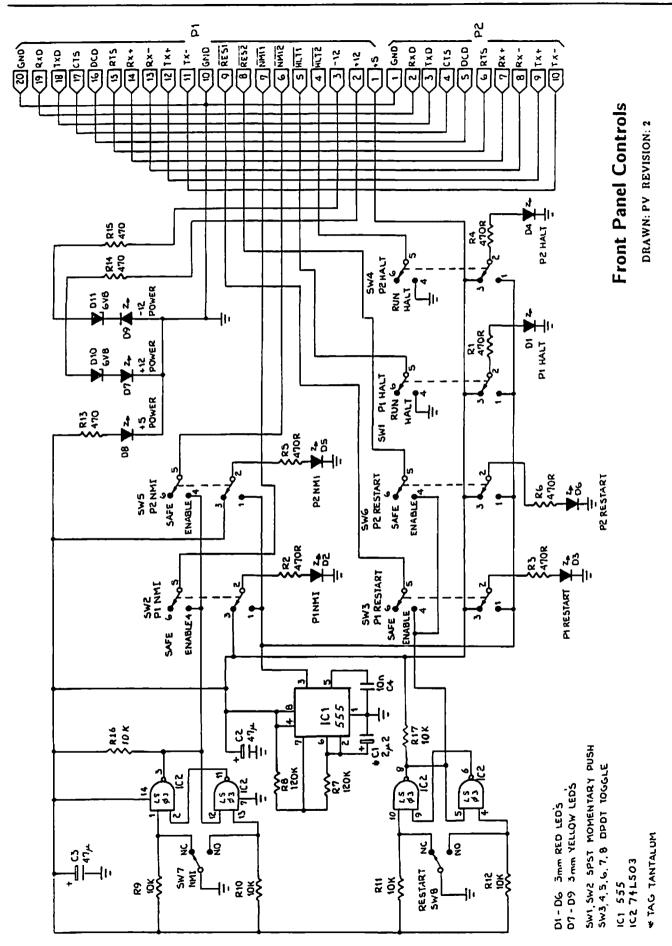

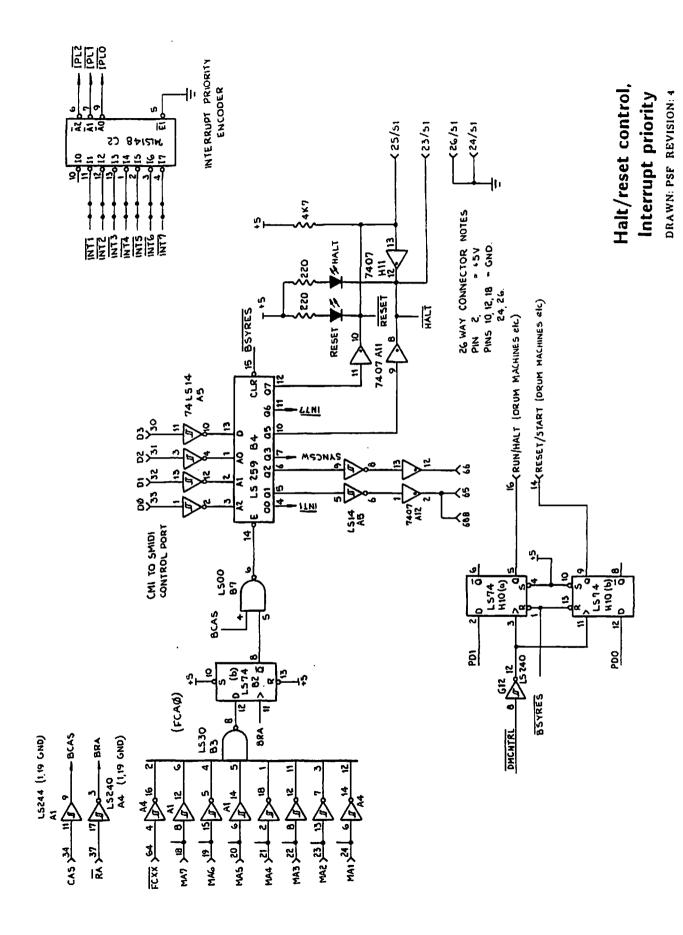

#### Manual Controls

Restart, halt and interrupt controls are provided on the front-panel card Q137. The sole use is for system debugging. In normal use all signals from the Q137 are inactive.

Activating either HALT switch on the front panel sends /HLT1 or /HLT2 to the corresponding processor on the Q209 CPU. When halted, the Buss Available signals from the CPU card W1 and W2 drive open-collector buffers B12 to turn on the WAIT LEDs on the card.

The system can run without a front panel being connected.

#### Power-on Reset

555 Timer A12 is used to generate a system-reset signal on power-up or manual restart from the front panel console, if restart is enabled on both processors. This is a low-going pulse of about 500 milliseconds on buss pin 42.

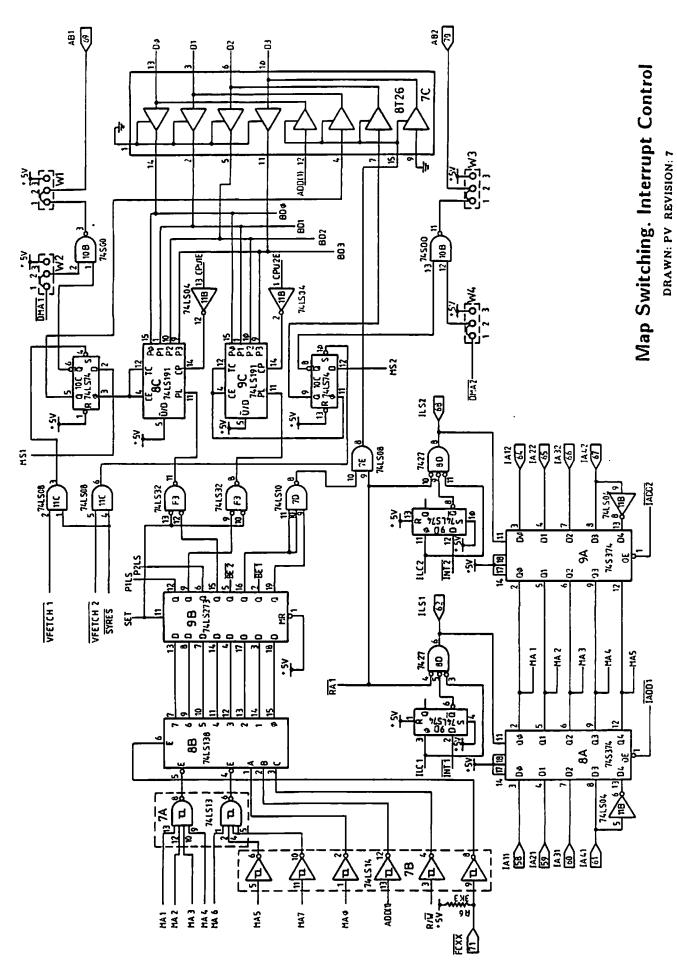

#### Interrupt Priority Logic

8214 Priority Interrupt Control Units (PICU) are used to latch interrupt requests and generate a priority level which is used by the CPU card to create an interrupt vector address. Each processor has its own PICU.

The priority level for each PICU is established by writing the complement of the desired priority level into the status register. The address for CPU 1 is FCFD, for CPU 2 it is FCFC. Decoding for this purpose is performed by one-of-eight selector B8.

Interrupt requests generated by the PICU are latched by flip-flops B9, which are reset when the PICUs are written to to establish the new priority level mask.

The PICUs are clocked by Interrupt Latch Strobe signals from the bus (ILS1 and ILS2).

Each PICU supports up to eight levels of interrupt.

twirlight

Memory Refresh DRAWN: PV REVISION: 7

## **Q256** 256K Ram Card

## 2.4

| Introduction          | 2.4.2   |

|-----------------------|---------|

| Options               | 2.4.2   |

| Map selection logic   | 2.4.3   |

| Address translation   | 2.4.4   |

| Memory block decoding | 2.4.6   |

| Bus interface         | 2.4.6   |

| Parity system         | . 2.4.6 |

| Memory Array          | 2.4.7   |

| Schematic diagrams    | 2.4.8   |

Note - In this document active low signals are indicated by a slash (/) in front of the signal name. This document is updated for the Rev. 2 Q256.

### Introduction

The Q256 is a 256K x 9 bit dynamic RAM, organised as four blocks of 64K and mapped in 2 or 4K chunks. 32 different mappings from "processor space" to physical memory space may be set up. The mapping selected for any given cycle is automatically switched according to the current machine state. The machine state comprises which processor is on the buss, the user state/system state output of the processor, and which DMA channel is active, if any.

The ninth bit in the memory is a parity bit. Parity generation takes place automatically upon writing to the RAM and parity error detection is automatic when reading. If a parity error is detected, an interrupt is generated. A status register records that a parity error occurred, the physical memory block in which it occurred, and the upper five bits of the processor address which was active at the time of the error. The error status bit is automatically cleared after the register has been read.

The map selection logic also generates three control signals: 1) PENB is a universal buss signal which enables or inhibits access to all peripherals on the buss. This signal is fed via the motherboard back into the Q256 since the map selection logic and the mapram are themselves peripherals. The output signal is forced active after power up to ensure configuration of the mapping system is possible, and released by the first read of the parity status register.

- 2) VENB is a video RAM enable bit which allows accesses in the range \$8000 to \$BFFF to read or write to the graphics RAM or user RAM which may be mapped into this area instead.

- PERGEN is a bit used to artificially generate parity errors to for testing purposes.

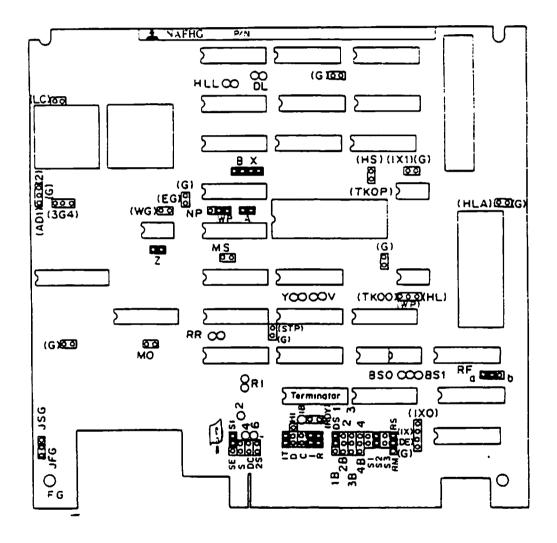

### Options

Option blocks WI and W2 allow selection of mapping on 2K or 4K byte boundaries as marked on the component overlay. If 4K mapping is selected, every second double-byte mapram location is not used. WI and W2 must be configured identically. Default links on the PCB are for 2K mapping.

Option block W3 is for debugging purposes and need only be installed if a faulty card is crashing the data buss of the test machine. The default PCB link to +5V must be cut. There are two non-default options. Option 3 (GND) permanently inhibits the data buss driver buffer. The memory can still be written to but read data will only get as far as the buss output buffer. This facility allows the operating system to boot and test programs to run on a healthy board while the faulty board runs in parallel without driving the data buss e.g. for signature analysis.

Option I enables the data buss permanently and is not normally used. The default link to DBEN prevents the buss driver from outputting data only until the first read from the status register. This allows the restart ROM program to initialize the memory mapping before enabling memory mapping.

A four-way DIP switch is provided to allow multiple Q256 boards to be installed. Only switches 1-3 are used, so up to 8 boards can be installed. Close a switch for each zero in the board number, i.e. card 0 has all switches closed. SWI is the LSB.

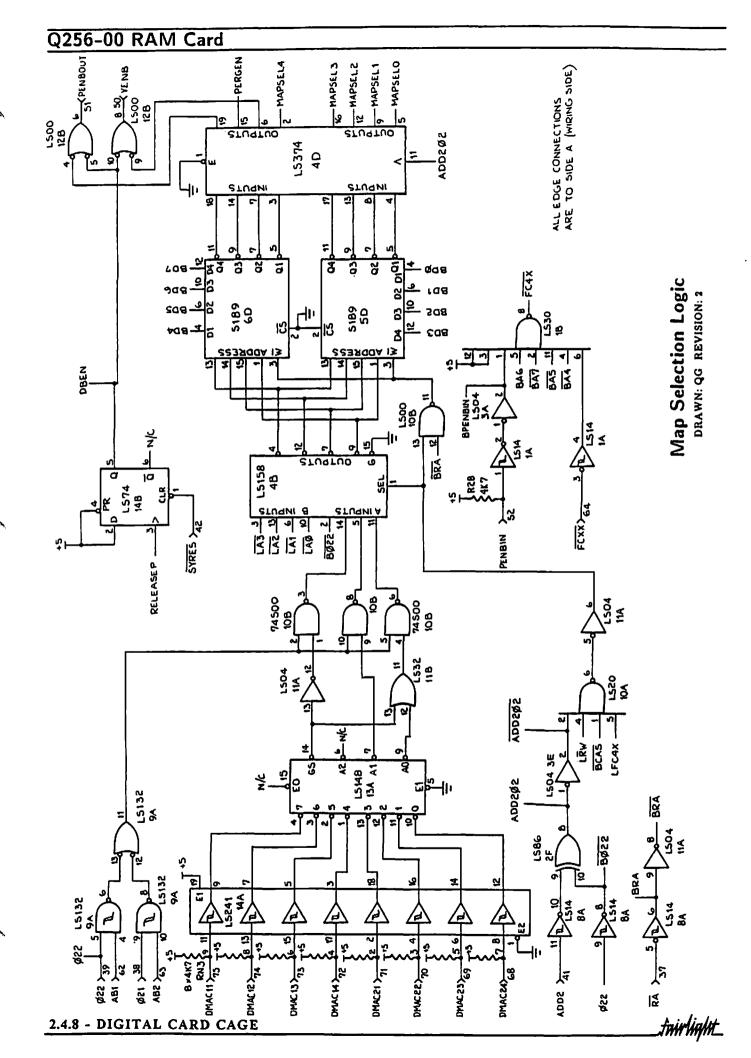

### Map Selection Logic

(refer schematic Q256-00)

The function of the map selection logic is to encode the current system state and generate a five-bit map selection number. It also generates the peripheral enable output signal (PENBOUT), the video ram enable signal (VENB) and a parity error generate signal (PERGEN) which forces an artificial parity error for testing purposes.

There are six possible states for each processor:

A or System state, no DMA

B or User state, no DMA

DMA on any one of four DMA channels. (Processor automatically switches to A state for DMA cycles).

The A/B/DMA state is encoded as three bits and the processor phase signal is added as a fourth bit and presented as an address via the multiplexor IC 4B to the map selection RAM (mapsel) ICs 5D and 6D. Thus each state corresponds to a location in the mapsel and its output data is the map selection number.

DMA claim signals (DMACpn, where p=processor and n=DMA channel) occur when a DMA peripheral has received a DMA acknowledge from the processor and arrive during the data phase preceding the actual DMA cycle. IC 13A is an 8 to 3 line encoder but since there are four channels for Pl and four for P2 the most significant output line only duplicates the processor phase signal and is not used. The GS output indicates that some DMA channel is active. Each processor has its own A/B line (ABl and AB2). The nand multiplexor 9A selects whichever is relevant for the next cycle. This signal, plus the combinatorial logic of 10B, 11A and 11B and the buffered phase signal  $(B\phi22)$  provide the four-bit state number to the multiplexor 4B.

The mapsel RAM occupies locations FC40-FC4F. Since there are six possible states per processor only twelve locations are actually used, as follows:

FC40 P2 B state FC43 P2 A state, no DMA P2 A state, DMA channel 1 FC44 FC45 P2 A state, DMA channel 2 FC46 P2 A state, DMA channel 3 P2 A state, DMA channel 4 FC47 FC48 PI B state FC4B Pl A state, no DMA FC4C Pl A state, DMA channel l FC4D PI A state, DMA channel 2 FC4E PI A state, DMA channel 3 FC4F PI A state, DMA channel 4

Access to these locations for initialization of the mapsel is decoded by IC 1B, along with the peripheral enable input PENBIN. The output of IC 1B is latched on rising BRA by IC 4A (drawing Q256-03) to produce LFC4X.

Writing to the mapsel RAM is the most time-critical of all operations on the Q256. Normally the entire current data phase is available to generate the map selection number for the next cycle but when writing, the current data phase must be used to write to the mapsel ram as well. This is achieved by making mapsel write cycles very short. To choose locations within \$FC4X the mapsel address multiplexor IC 4B is switched over to the lower four latched address bits on the falling edge of ADD2\(\text{\theta}\)2 (data and address busses are in phase). The data is written into the mapsel ram on the rising of \(\text{BRA}\) (IC 10B). The write pulse is removed and the multiplexor switched back to the current state number only 50nS later by the falling of \(\text{BCAS}\) (IC 10A).

The lower five bits of the mapsel RAM are the map select number (MAPSEL0-4). This plus the controls PENBOUT, VENB and PERGEN are latched on the rising of ADD2ø2 which begins the next address cycle.

The peripheral enable signal (PENBOUT) and the graphics enable (VENB) come from bits 7 and 5 of the mapsel ram respectively. After power up or system reset they are both forced active (high) by the flip-flop IC 14B so that access to the mapsel ram is ensured for initialization. This flip-flop also inhibits the data buss driver IC 9B (drwg Q256-03) if W3 has been linked to option 2 for debugging. The flip-flop is triggered as soon as either processor reads the parity status register and will remain set until the next SYRES.

Format of data written to the mapsel RAM is as follows:

Bit 0-4 Map select number MAPSEL0-4. (Inverted)

- 5 VENB (Write 0 to enable graphics ram)

- 6 PERGEN (Normally 0, 1 to force a parity error)

- 7 PENBOUT (Write 0 to enable peripherals)

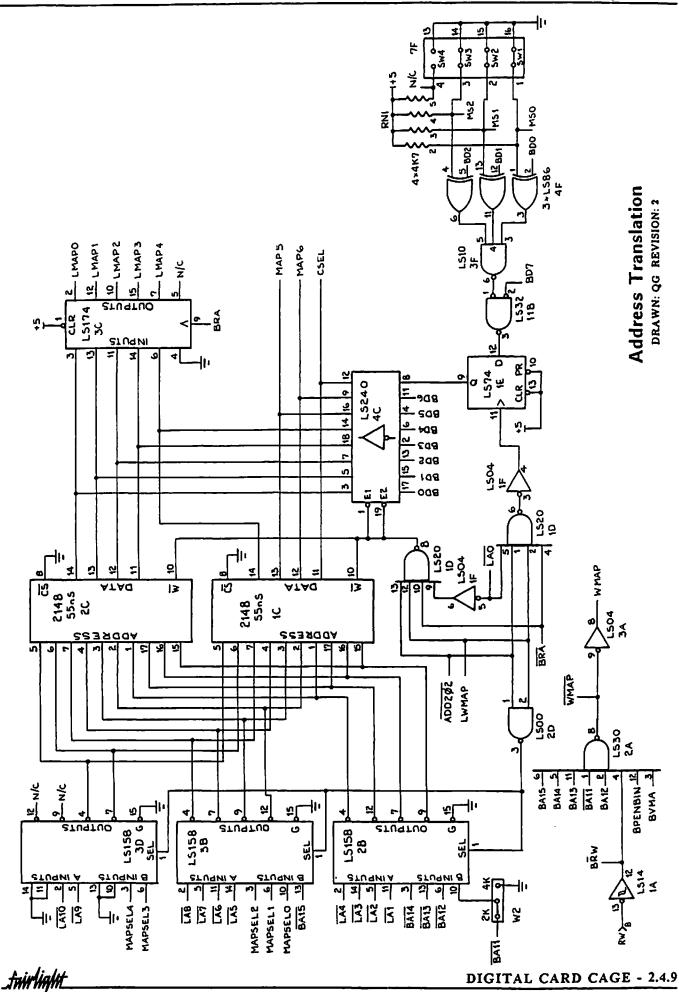

### Address Translation

(refer to Drawing Q256-01)

This section performs the mapping from the 64K processor address space onto the 256K physical address space. The outputs LMAP0-4 and MAP5,6 plus standard address lines MA0-10 constitute the 18 bit address required to uniquely access any location in 256K.

All mapping data is stored in the two 2148 static RAMs (mapram), each containing 1024 x 4 bits. If 2K mapping is selected, the lower five address lines of the mapram come from the upper five processor address bits via multiplexor ICs 2B, 3B and 3D. This divides the 64K processor space into 32 blocks of 2K each. In 4K mode only the top 4 processor lines are used and the LSB of the mapram address is ticd low. The upper five mapram address lines come from the latched map select number, thus any one of 32 different complete mappings may be selected. The data outputs from the mapram include a card select bit (CSEL), a two-bit 64K rank select (MAP5,6), and a five bit page select which is latched on rising BRA (LMAP0-4). The page select bits become the upper physical address bits.

Although the mapram is 1K bytes in size it in fact occupies 2K of address space, from \$F000-F7FF. Even locations in this range are dummy locations which serve only to set up the CSEL flip-flop, IC 1E. Writes to odd locations then store this single bit along with 7 bits of mapping data in the mapram. So a single 16-bit write to the mapram maps one 2K or 4K page of processor space to any 2K or 4K physical page in the 256K available. The processor space being mapped is determined by the address within \$F000-F7FF written to and the physical page selected is given by the data written.

Valid addresses in the mapram range are decoded with the buffered peripheral enable signal (BPENBIN) by IC 2A and the write map (WMAP) signal is latched by IC 4A (drwg Q256-03). The mapram address lines are switched over to LA1-LA10 on the rising of  $\overline{ADD2}$ 62 by IC 2D. The 2148s have common data-in and data-out lines multiplexed by the write  $(\overline{W})$  input. If an odd address is being written, the buffered data buss is driven into the 2148s from IC 4C and the  $\overline{W}$  input strobed by the upper LS20, IC  $\overline{D}$  1D on the rising of  $\overline{D}$  3RA. The write pulse is terminated by falling  $\overline{ADD2}$ 62, and data hold time to the 2148s is provided by the disable delay of IC 4C.

Writing to an even address triggers the CSEL flip flop IC IE on rising BRA. The data to this flip flop is the result of the three-bit comparison of BD0-2 with the card select no. set up on the DIP switch, qualified by BD7 which may be used as an overall page enable bit. Thus mapram data format is as follows:

Even locations

Bit 7 Page enable Bits 5-3 Unused Bits 2-0 Card select

Odd locations

Bit 7 Unused

Bits 6,5 Physical 64K block select

Bits 4-0 Physical 2K block select

(Bit 0 not used in 4K mapping configuration)

Note that when mapping multiple pages of memory in or out the CSEL flip-flop need only be set up once, after which only writes to odd locations in mapram are required.

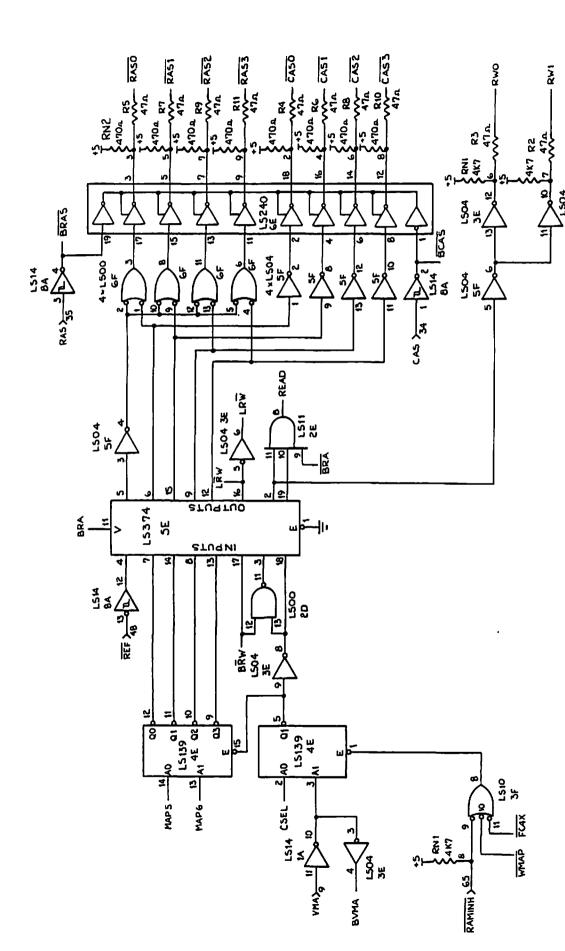

### Memory Block Decoding (refer schematic Q256-02)

This section generates RAS and CAS controls for each of the four memory ranks according to mapping outputs MAP5,6 and the card select signal CSEL.

MAP5,6 are decoded to a 1-of-4 block select signal by IC 1E provided a valid address is on the buss (VMA), the Debug's Ram inhibit (RAMINH) is inactive, and neither \$FC4X nor the mapram are being accessed. IC 5E latches this select along with the refresh signal REF, read/write (mapsel, mapram, or status), read/write memory, and access memory signals on rising BRA. IC 2E generates the READ signal to drive the data buss while BRA is high (see drwg Q256-03).

Refresh cycles cause the system RAS signal to be distributed to all four memory ranks simultaneously through ICs 6F and 6E. No rank select and thus no CAS is generated during refresh cycles. During a valid memory access one rank is selected and CAS is routed to that block through ICs 5F and 6E. The R/W signal drives all ranks through ICs 5F and 3E.

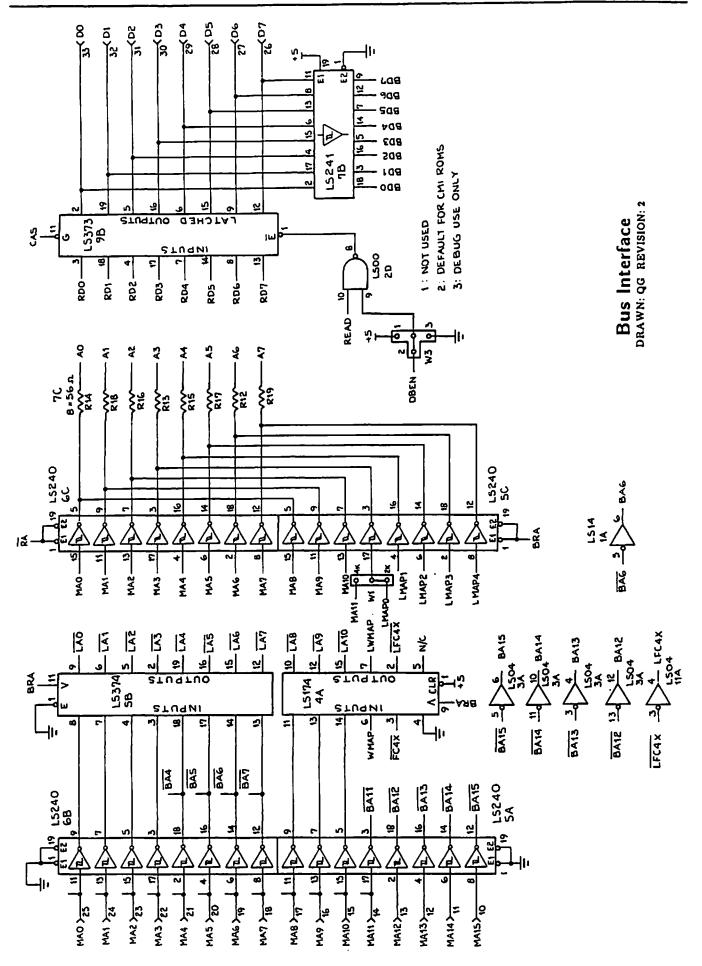

### **BUSS** Interface

(refer schematic Q256-03)

The buss address lines are buffered by ICs 6B and 5A and latched on rising BRA by ICs 4A and 5B for mapram and mapsel ram writing and status register reading, along with address decode signals WMAP and  $\overline{FC4X}$ .

Unmapped address lines MA0-10 (and MA11 in the 4K mapping configuration) plus mapping outputs LMAP0-LMAP4 (excluding LMAP0 for 4K mapping) are multiplexed onto the RAM address lines by ICs 5C and 6C.

IC 9B latches the RAM outputs on the falling edge of CAS and drives the buss when READ is high unless the debug option W3 prevents this. Data is buffered off the buss to mapsel, mapram, main RAM and parity generator by IC 7B.

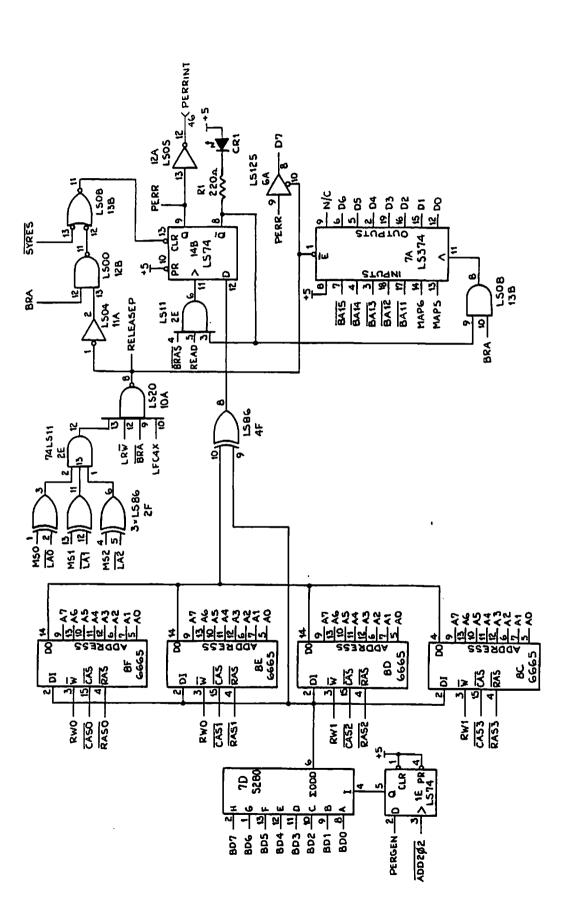

### Parity System

(refer schematic Q256-04)

The parity bit is automatically generated by IC 7D from the data on the buss when writing to RAM. This bit is written into the appropriate 6665 when the corresponding CAS signal is generated (see drawing Q256-02).

A RAM read cycle causes the parity bit from the selected block to be read out of the parity RAM while IC 7D simultaneously regenerates the same parity bit from the data actually leaving the main RAM and coming back in again through data buffer IC 7B. Thus parity errors may be caused by buss errors as well as RAM faults. The parity memory bit and the regenerated parity bit are compared by exclusive or gate IC 4F. The result of this comparison is only valid for about 150nS and is clocked by rising BRAS into flip flop 14B to generate the parity error interrupt (PERRINT) and the parity error status bit (PERR). Further clocking to the flip flop is disabled by the Q output going low.

On each RAM cycle, the rank select lines MAP5, 6 and 5 upper processor address lines are latched by IC 7A. As soon as a parity error occurs this latching is disabled by the /Q output of the parity flip-flop so that the physical block and the processor 2K address space in which the error occurred is recorded.

The parity system status register occupies the same space as the mapsel RAM: FC40 to FC4F. (The mapsel is write only, the status register is read only). The lower 3 bits of the latched address are compared with the module select lines MS0-2 from the DIP switch by IC 2F so that in a multi-card system parity registers on cards 0-7 are at FC40-7 respectively. A read from the status register enables the latch 7A and buffer 6A onto the data buss on the rising of /BRA and the parity error is cleared by a very short pulse (approx 20nS) on the rising of BRA at the termination of the read cycle. The flip flop is also cleared automatically by /SYRES.

The parity error generate signal PERGEN is used to artificially create a parity error for testing purposes. The I input of IC 7D is simply a ninth data input so that if it is 0 when a RAM location is written it must also be 0 when that location is read, otherwise an "error" will be generated. When testing the parity system, a location is written with the I input 0 and the read back just as the I input is switched to 1. PERGEN is the control for this and comes from the mapsel logic. Since the mapsel outputs are of a lookahead nature, the PERGEN signal is delayed by half a cycle by first latching on rising ADD2\(\phi\)2 at IC 4D then clocking on rising /ADD2\(\phi\)2 at flip flop IC1E.

In the diagnostic tests the A state is initialised with PERGEN reset and the B state is initialised with PERGEN set. After writing a location in the A state, the processor switches to the B state at the instant of reading back the location.

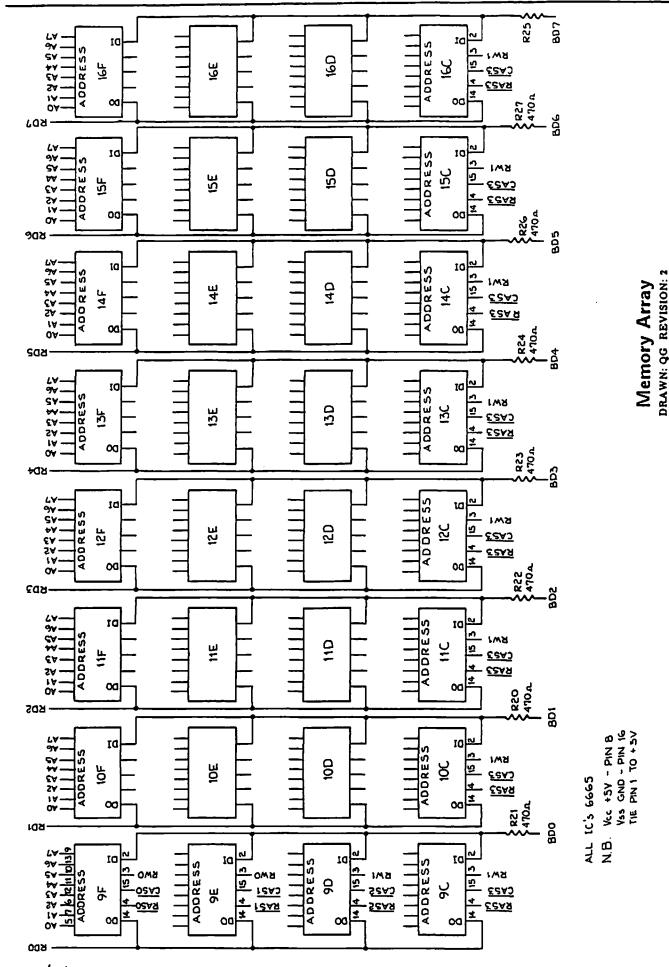

### Memory Arrary

(refer schematic Q256-05)

The dynamic memory array consists of four ranks of nine RAM ICs. Each IC is a 64K x 1 bit device, so each rank forms one byte plus parity bit. Which rank is accessed depends on which /RAS and /CAS lines are driven low by the decoding circuitry.

The RAM chips each have 8 address lines. Since 64k space requires 16 address bits the full address is multiplexed onto the 8 lines. The lower 8 bits ("Row" address) is latched into the RAM chips when /RAS goes low. After a period of address hold time the address multiplexor switches over and drives the upper 8 bits ("Column" address) into the RAMs. This is latched into the RAMs when /CAS goes low.

During a write cycle, data is latched into the RAMs on the falling edge of /CAS. In the case of a read cycle, data out becomes valid within 75nS of the falling edge of /CAS. The data lines are driven by the selected rank of RAMs while /CAS is low, and go tri-state at other times.

The state of the /W signal while /CAS is low determines whether the cycle is read or write.

Due to the capacitive input impedance of the MOS RAM ICs, the address and data input lines are driven through series resistors to limit the voltage undershoot.

Memory Block Decoding DRAWN: 9G REVISION: 2

.tairlight\_

MONS ACCESS TIME 2148'S MAY BE USED AT IC AND 2C PROVIDED AN 5139 IS USED AT 4E

NOTE

\_tairlight\_

Parity System DRAWN: QG REVISION: 2

tairlight

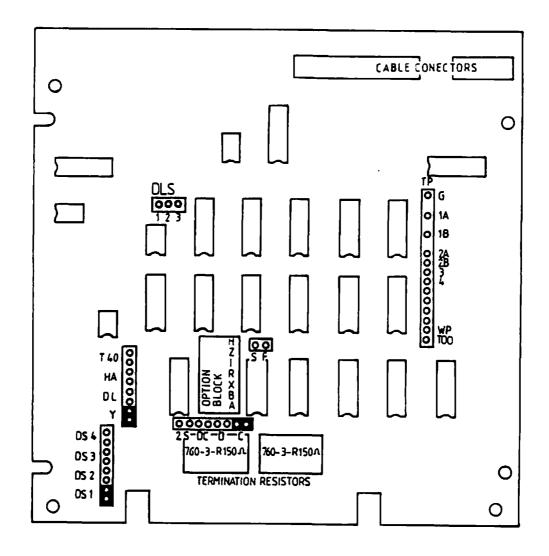

# QFC9 Floppy Disc Controller

## 2.5

| Introduction               | 2.5.2 |

|----------------------------|-------|

| Address map                | 2.5.3 |

| Commands                   | 2.5.4 |

| DMA address counter        |       |

| DMA BYTE transfer counters | 2.5.4 |

| Data buffers               |       |

| Address decoding           |       |

| Controller LSI             |       |

| DMA logic                  |       |

| Control register           |       |

| Master oscillator          |       |

| Write recompensation       |       |

| Data Separator             |       |

| Device driver ROM          |       |

| Schematic diagrams         |       |

|                            |       |

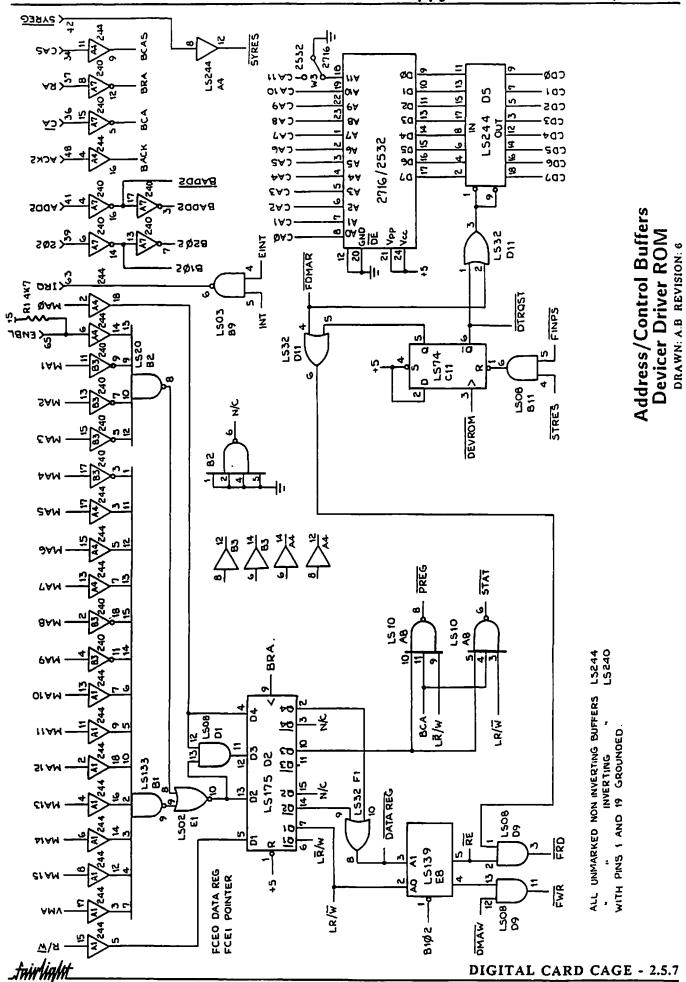

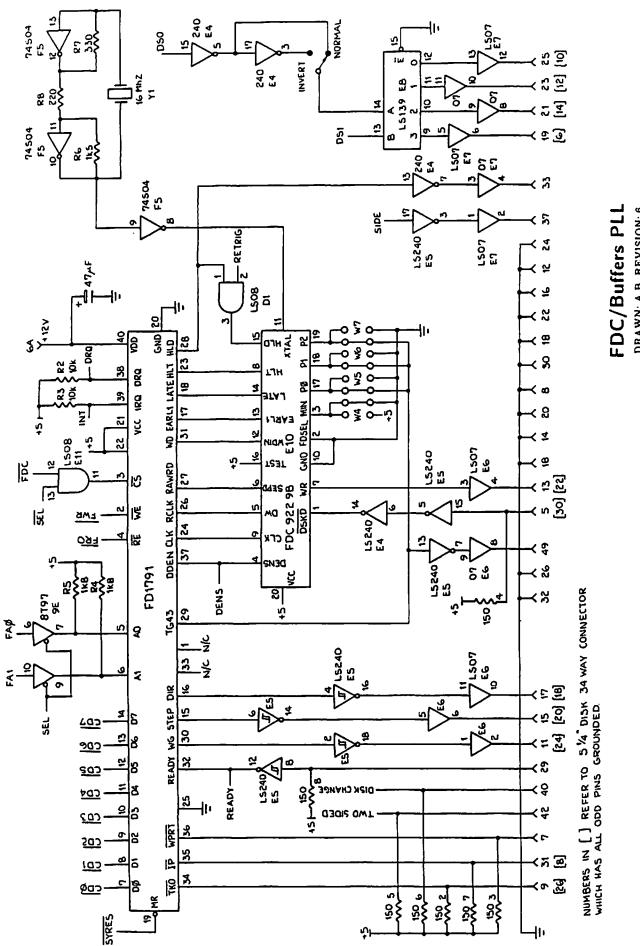

### Introduction

The floppy interface card interfaces the bit parrallel/serial buss of floppy disk drives to the CMI's interleaved parellel buss. The interface is a combination of device driver software, controlling disk data format and initialization of data transfer parameters, and the hardware which carries out the transfers without processor intervention.

Data is stored on the floppy disk itself on its magnetic coating, in concentric rings. In a standard, 8 inch floppy there are 77 such rings on each side called tracks. Tracks are divided into data blocks called sectors. Sectors in Fairlight disk formats are either 128 or 256 bytes per sector, depending on operating system being used. The smallest amount of data that can be read to or from a disk is one sector. Sectors on a disk may be randomly accessed.

Track 0 is outermost. The controller automatically restores to this track on power on, and on reaching track 0, signals the controller by a mechanical switch generated signal. All head movement is relative to this reset state.

Floppy drives transfer data serially. They also have parallel control lines to control drive number selection, head stepping direction, head load, disk write and disk write enable. The head of the drive must be lowered to the disk surface before a transfer may take place, this is operation refered to as "head load". Index pulses are generated by the drive so that the controller knows the location of the rotating disk. This pulse occurs once per revolution, so the start of tracks can be determined by the controller. Also, the controller generates pulses that are used to step the head in and out to position it over the required ack.

The Floppy Disk Controller/Formatter uses the WD1791 LSI controller. It is software selectable to double density, double sided in addition to single density, single sided. It is designed to work with CPU #2's, transferring data to and from memory by DMA on Processor 2. The processor is not involved with transferring data to and from the disk. Once a data transfer is set up the processor may continue processing other tasks until the interupt for "command complete" is issued by the controller.

### Address Map

(refer schematic QFC9-01)

The controller is accessed through two locations, in a memory map which enables access to peripherals. An address register is set up to point to the required controller register. All data is read or written through a single data register.

| ADDRESS (HEX) | READ            | WRITE            |

|---------------|-----------------|------------------|

| FCE0          | data            | data             |

| FCE1          | status register | address register |

The 7 controller registers are:

- 00 control register

- 02 DMA address (low byte)

- 04 DMA address (high byte)

- 06 byte count to read/write (low byte, inverted)

- 08 byte count to read/write (high byte, inverted)

- 0A command location to load device driver ROM into RAM WD1791 L.S.I

- 0C cmd (write) status (read)

- 0D track

- 0E sector

- 0F data

The definitions of the control register bits are:

- 0 DS0 drive select address bit 0

- 1 DS1 drive select address bit 1

- 2 enable interrupt (active high)

- 3 enable DMA address incrementing (active low)

- 4 DMA transfer direction (1= to disk)

- 5 side select

- 6 retrig head load timer

- 7 DENS density selection

### The definitions of the control status bits are:

- 0 0

- 1 n/c

- 2 n/c

- 3 ready

- 4 two sided

- 5 disk change

- 6 interrupt

- 7 device driver loading (active low)

### Commands

The extensive instruction set of the 1791 LSI can be obtained from the manufacturers data sheets for the 1791. This device handles all data conversions between the disk drive and the CMI buss.

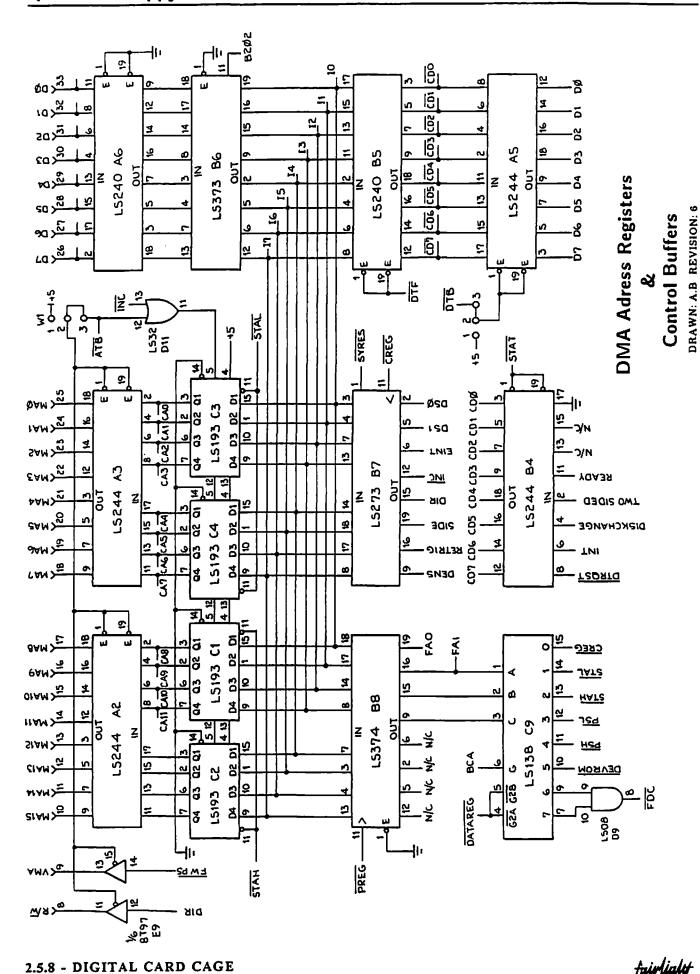

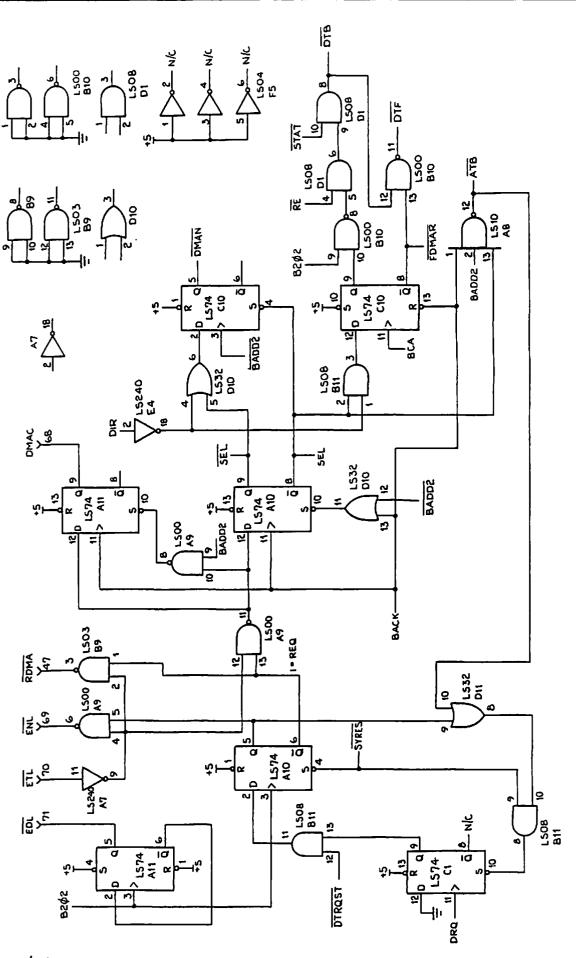

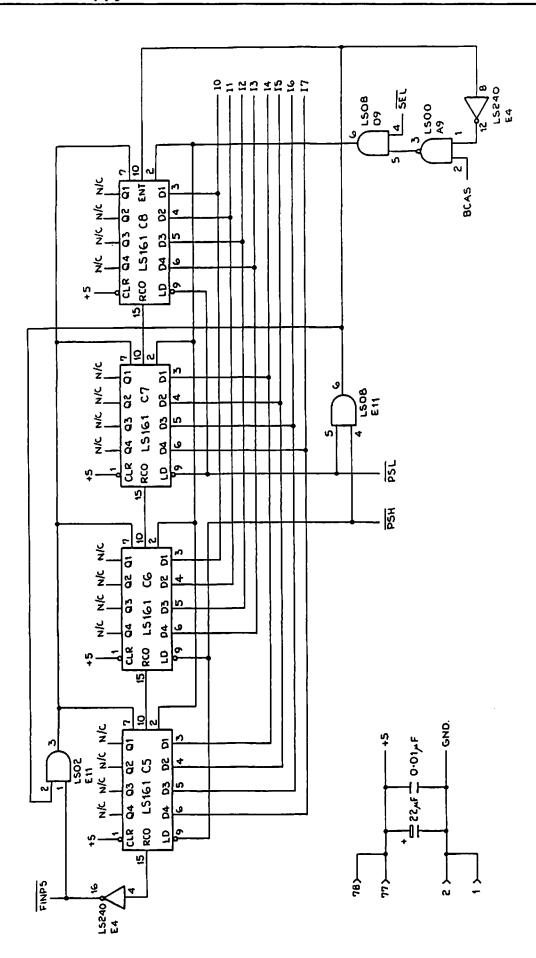

### DMA address Counters

(refer schematic QFC9-02)

Sixteen bit counter chain C1 to C4 is used to provide the address for DMA transfers. The starting address for each disk transfer is established by writing the appropriate byte address to the address register then writing the address byte to the data register and then repeating for the other address byte. This causes the address to be preset into the DMA address counters by means of parallel-load strobe pulses STAL (low byte) and STAH (high byte). The incrementing of the DMA counters may be inhibited under software control, so that disk data may be dumped directly into the data portholes on channel cards.

### DMA Byte Transfer Counters

(refer schematic QFC9-04)

Sixteen bit counter chain C5 to C8 is used to transfer the required number of bytes to or from disk. It must be initialized with the inverse of the number of bytes to be transfered. Any number may be specified up to a maximum of 65,535 bytes. Only those bytes specified will be transferred to memory on a disk read. This allows less than a sector to be read from disk, and saves the software overhead required to handle partial sector reads. The read takes place but the buss VMA signal goes inactive after the required number of bytes have been transferred, so disabling memory writes. The VMA disable signal is generated from the ripple carry out on this counter chain, by buffering /FINPS, (Finished Partial Sector).

When a transfer occurs, the DMAC (Direct Memory Access Claim) line is generated so that the memory card swaps maps, allowing data to be dumped into memory currently not mapped into the processor's address space. This signal is generated by the components around flip-flop A11.

### Data Buffers

(refer schematic QFC9-02)

Data is propagated from the system data bus via latch B6 which hold the data across the processor I phase. This latched data also becomes the DATA FROM BUS via buffer B5, to the floppy-controller LSI.

Data written to the system control register at 00 is latched by B7. This controls such functions as drive select and DMA direction.

### Address Decoding

Address range \$FCE0-\$FCE1 is decoded by gates B1, E1, B2, E1 and latched by D2.

Address \$FCE0 is used to enable the internal data buss to read and write to controller functions.

Address \$FCE1 data is latched by B8 and with the access to FCE0 generates the internal chip selects and read/write strobes through C9.

Inverting buffer E5 and open collector drivers E6, E7 are used to interface the 1791 LSI controller to the disk drive cable. Incoming disk status signals are pulled up by 150 ohm terminating resistors.

### Controller LSI

The Interupt Request from the LSI is gated with the Interupt Enable to provide an open-collector interupt signal for the system I.R.Q. on buss pin 63A.

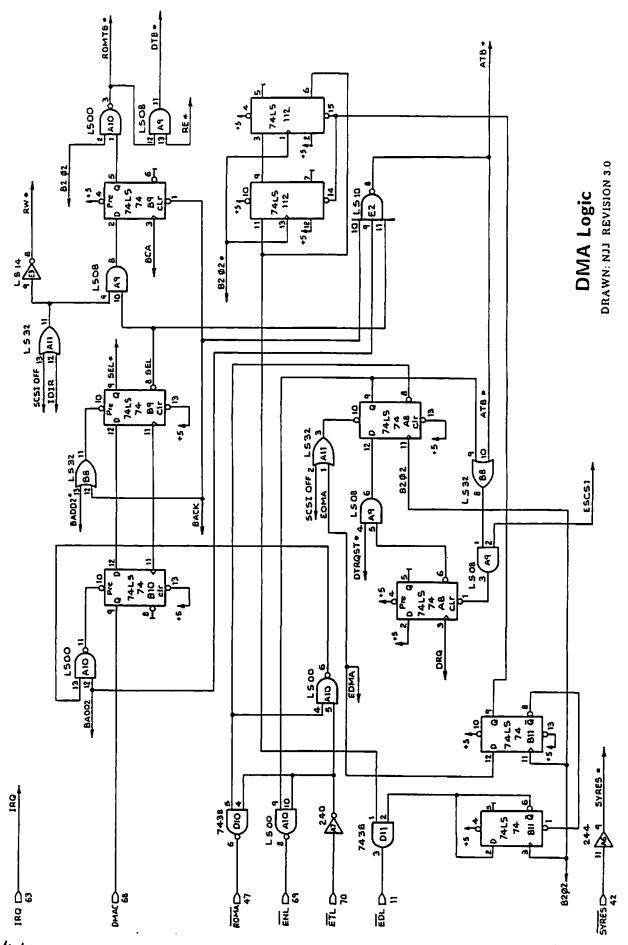

### DMA Logic

(refer schematic QFC9-03)

Data requests from the 1791 or Device Driver rom loading are synchronised with Processor 2 Phase 2 using flip-flops C1 and A10. This sets up a DMA request to the processor (RDMA).

DMA cycles are granted by ACK acknowledge signal.

Flip-flop All only allows a DMA cycle to occur every second Processor cycle (the floppy drive can not transfer at that rate but this is a system constraint on other DMA devices in the DMA daisy chain).